ARTIX-7 FPGA

Papan Inti

AC7A200

Sistim on Module

Manual pamaké

Rékam Vérsi

| Vérsi | titimangsa | Dileupaskeun Ku | Katerangan |

| Wahyu 1.0 | 28-06-20 | Rachel Zhou | Kaluaran munggaran |

Bagian 1: AC7A200 Inti Board Perkenalan

AC7A200 (modél dewan inti, sarua handap) dewan inti FPGA, eta dumasar kana XILINX urang ARTIX-7 runtuyan 100T XC7A200T-2FBG484I. Ieu papan inti-kinerja luhur kalawan speed tinggi, rubakpita tinggi jeung kapasitas tinggi. Éta cocog pikeun komunikasi data-speed tinggi, ngolah gambar video, akuisisi data-speed tinggi jsb.

dewan inti AC7A200 Ieu ngagunakeun dua lembar chip MT41J256M16HA-125 DDR3 MICRON urang, unggal DDR boga kapasitas 4Gbit; dua chip DDR digabungkeun kana 32-bit lebar beus data, jeung baca / nulis rubakpita data antara FPGA na DDR3 nepi ka 25Gb; konfigurasi misalna bisa minuhan kaperluan processing data rubakpita tinggi.

Papan inti AC7A200 ngalegaan 180 palabuhan IO standar tingkat 3.3V, 15 palabuhan IO standar tingkat 1.5V, sareng 4 pasang sinyal diferensial RX / TX kecepatan tinggi GTP. Pikeun pangguna anu peryogi seueur IO, papan inti ieu bakal janten pilihan anu saé. Leuwih ti éta, routing antara chip FPGA sarta panganteur nyaeta panjangna sarua jeung processing diferensial, sarta ukuran dewan inti ngan 2.36 inci * 2.36 inci, nu cocog pisan pikeun ngembangkeun sekundér.

Angka 1-1: Papan Inti AC7A200 (Harepan View)

Angka 1-2: Papan Inti AC7A200 (Pungkur View)

Bagian 2: Chip FPGA

Sakumaha anu disebatkeun di luhur, modél FPGA anu kami anggo nyaéta XC7A200T-2FBG484I, anu kalebet dina séri Artix-7 Xilinx. Kelas laju nyaéta 2, sareng kelas suhu nyaéta kelas industri. Modél ieu mangrupikeun pakét FGG484 sareng 484 pin. Xilinx ARTIX-7 FPGA chip aturan ngaran sakumaha dihandap

Gambar 2-1: Harti Modél Chip Spésifik tina séri ARTIX-7

angka 2-2: chip FPGA on dewan

Parameter utama chip FPGA XC7A200T nyaéta kieu

| Ngaran | Parameter khusus |

| Sél Logika | 215360 |

| keureutan | 16-02-92 |

| CLB flip-flops | 269200 |

| Blok RAM (kb) | 13140 |

| DSP keureutan | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC, 12bit, 1Mbps AD |

| GTP Transceiver | 4 GTP, 6.6Gb/s maks |

| Kelas Laju | -2 |

| Kelas Suhu | Industri |

Sistim suplai kakuatan FPGA

Catu daya Artix-7 FPGA nyaéta VCCINT, VCCBRAM, VCCAUX, VCCO, VMGTAVCC sareng VMGTAVTT. VCCINT mangrupikeun pin catu daya inti FPGA, anu kedah dihubungkeun sareng 1.0V; VCCBRAM teh catu daya pin of FPGA Blok RAM, nyambung ka 1.0V; VCCAUX nyaéta pin catu daya bantu FPGA, nyambungkeun 1.8V; VCCO nyaéta voltage unggal BANK FPGA, kaasup BANK0, BANK13~16, BANK34~35. Dina papan inti FPGA AC7A200, BANK34 sareng BANK35 kedah dihubungkeun sareng DDR3, voltage sambungan BANK nyaeta 1.5V, sarta voltage BANK séjén nyaéta 3.3V. VCCO of BANK15 na BANK16 ieu Powered by LDO, sarta bisa dirobah ku ngaganti chip LDO. VMGTAVCC nyaéta suplai voltage tina transceiver GTP internal FPGA, disambungkeun ka 1.0V; VMGTAVTT nyaéta terminasi voltage tina transceiver GTP, disambungkeun ka 1.2V.

Sistem FPGA Artix-7 merlukeun urutan kakuatan-up jadi kakuatan ku VCCINT, lajeng VCCBRAM, lajeng VCCAUX, sarta tungtungna VCCO. Lamun VCCINT na VCCBRAM boga vol saruatage, aranjeunna tiasa Powered up dina waktos anu sareng. Urutan kakawasaan outages dibalikkeun. Runtuyan power-up tina transceiver GTP nyaeta VCCINT, lajeng VMGTAVCC, lajeng VMGTAVTT. Lamun VCCINT na VMGTAVCC boga vol saruatage, aranjeunna tiasa Powered up dina waktos anu sareng. Runtuyan kakuatan-off ngan sabalikna tina runtuyan kakuatan-on.

Bagian 3: Kristal diferensial aktip

Papan inti AC7A200 dilengkepan dua kristal diferensial aktif Sitime, hiji nyaéta 200MHz, modélna nyaéta SiT9102-200.00MHz, sistem jam utama pikeun FPGA sareng dianggo pikeun ngahasilkeun jam kontrol DDR3; nu sejenna nyaeta 125MHz, model nyaeta SiT9102 -125MHz, input jam rujukan pikeun transceiver GTP.

Bagian 3.1: jam Diferensial Aktif 200Mhz

G1 dina Gambar 3-1 nyaéta 200M kristal diferensial aktif nu nyadiakeun sumber jam sistem dewan ngembangkeun. Kaluaran kristal disambungkeun ka pin jam global BANK34 MRCC (R4 jeung T4) tina FPGA. Jam diferensial 200Mhz ieu tiasa dianggo pikeun ngajalankeun logika pangguna dina FPGA. Pamaké tiasa ngonpigurasikeun PLL sareng DCM di jero FPGA pikeun ngahasilkeun jam tina frékuénsi anu béda.

Angka 3-1: 200Mhz Active Differential Crystal Schematic

angka 3-2: 200Mhz Active diferensial Kristal on Board Core

200Mhz Diferensial Jam Pin Assignment

| Ngaran Sinyal | PIN FPGA |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

Bagian 3.2: 125MHz Active Diferensial Kristal

G2 dina Gambar 3-3 nyaéta kristal diferensial aktif 125MHz, nu mangrupakeun jam input rujukan disadiakeun pikeun modul GTP jero FPGA. Kaluaran kristal disambungkeun ka pin jam GTP BANK216 MGTREFCLK0P (F6) jeung MGTREFCLK0N (E6) tina FPGA.

angka 3-3: 125MHz Active diferensial Kristal Schematic

angka 3-4: 125MHz Active diferensial Kristal on Board Core

125MHz Diferensial Jam Pin Assignment

| Ngaran Net | PIN FPGA |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

Bagian 4: DDR3 DRAM

Papan inti FPGA AC7A200 dilengkepan dua chip Micron 4Gbit (512MB) DDR3 (sakabehna 8Gbit), modélna MT41J256M16HA-125 (cocog sareng MT41K256M16HA-125). DDR3 SDRAM boga speed operasi maksimum 400MHz (laju data 800Mbps). Sistim memori DDR3 disambungkeun langsung ka panganteur memori BANK 34 na BANK35 FPGA. Konfigurasi husus tina DDR3 SDRAM ditémbongkeun dina Table 4-1.

| Nomer Bit | Modél Chip | Kapasitas | Pabrik |

| U5,U6 | MT41J256M16HA-125 | 256M x 16 bit | Mikron |

meja 4-1: Konfigurasi DDR3 SDRAM

Desain hardware DDR3 merlukeun tinimbangan ketat ngeunaan integritas sinyal. Kami geus pinuh dianggap résistor cocog / lalawanan terminal, renik kontrol impedansi, sarta renik kontrol panjang dina rarancang sirkuit jeung desain PCB pikeun mastikeun-speed tinggi na operasi stabil tina DDR3. angka 4-1 rinci sambungan hardware DDR3 DRAM

angka 4-1: The DDR3 DRAM Schematic

angka 4-2: The DDR3 dina Board Core

Tugas pin DRAM DDR3:

| Ngaran Net | Ngaran PIN FPGA | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

Bagian 5: QSPI Flash

Papan inti FPGA AC7A200 dilengkepan hiji 128Mbit QSPI FLASH, sareng modélna N25Q128, anu nganggo 3.3V CMOS voltage standar. Kusabab sifat non-volatile tina QSPI FLASH, éta tiasa dianggo salaku alat boot pikeun sistem pikeun nyimpen gambar boot sistem. Gambar ieu utamana kaasup bit FPGA files, kode aplikasi ARM, kode aplikasi inti lemes sareng data pamaké séjén files. Model husus sarta parameter patali SPI FLASH ditémbongkeun dina Table 5-1.

| Posisi | Modél | Kapasitas | Pabrik |

| U8 | N25Q128 | 128M Bit | Numonyx |

meja 5-1: Spésifikasi QSPI FLASH

QSPI FLASH disambungkeun ka pin dedicated of BANK0 na BANK14 tina chip FPGA. Pin jam disambungkeun ka CCLK0 of BANK0, sarta data sejen tur chip pilih sinyal disambungkeun ka D00 ~ D03 na FCS pin BANK14 mungguh. angka 5-1 nembongkeun sambungan hardware QSPI Flash.

Gambar 5-1: QSPI Flash Schematic

Tugas pin Flash QSPI:

| Ngaran Net | Ngaran PIN FPGA | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

angka 5-2: QSPI FLASH on Board Core

Bagian 6: Lampu LED dina Papan Inti

Aya 3 lampu LED beureum dina papan inti AC7A200 FPGA, salah sahijina nyaéta lampu indikator daya (PWR), hiji lampu LED konfigurasi (DONE), sarta hiji lampu LED pamaké. Lamun dewan inti ieu Powered, indikator kakuatan bakal nyaangan; lamun FPGA geus ngonpigurasi, LED konfigurasi bakal caang. Pamaké lampu LED disambungkeun ka IO tina BANK34, pamaké bisa ngadalikeun lampu sareng mareuman ku program. Nalika IO voltage disambungkeun ka pamaké LED tinggi, pamaké LED nyaangan. Nalika sambungan IO voltage low, pamaké LED bakal dipareuman. Diagram skéma tina sambungan hardware lampu LED ditémbongkeun dina Gambar 6-1:

angka 6-1: lampu LED dina Core Board Schematic

angka 6-2: lampu LED dina Board Core

Pamaké LEDs Pin Assignment

| Ngaran Sinyal | Ngaran Pin FPGA | Nomer Pin FPGA | Katerangan |

| LED1 | IO_L15N_T2_DQS_34 | W5 | pamaké LED |

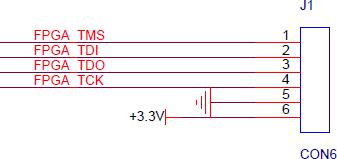

Bagian 7: JTAG Panganteur

The JTAG test stop kontak J1 ditangtayungan dina papan inti AC7A200 pikeun JTAG ngundeur tur debugging nalika dewan inti dipaké nyalira. Gambar 7-1 mangrupa bagian skéma tina JTAG port, nu ngawengku TMS, TDI, TDO, TCK. , GND, +3.3V genep sinyal ieu.

Gambar 7-1: JTAG Skématik panganteur

The JTAG panganteur J1 on AC7A200 dewan inti FPGA ngagunakeun 6-pin 2.54mm pitch single-baris liang test. Upami anjeun kedah nganggo JTAG konektor pikeun debug dina dewan inti, anjeun kudu solder a 6-pin single-baris pin lulugu.

Gambar 7-2 nunjukkeun JTAG panganteur J1 dina dewan inti AC7A200 FPGA.

Gambar 7-2 JTAG Interface on Board Core

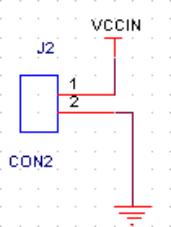

Bagian 8: Power Interface dina Board Core

Dina raraga nyieun AC7A200 FPGA core dewan dianggo nyalira, dewan inti ditangtayungan 2-pin panganteur catu daya J2. Upami pangguna hoyong debug fungsi dewan inti nyalira (tanpa dewan pamawa), alat éksternal kedah nyayogikeun + 5V pikeun nyayogikeun kakuatan ka dewan inti.

Gambar 8-1: Skématik Antarmuka Daya dina Papan Inti

Gambar 8-2: Antarbeungeut kakuatan dina Papan Inti

Bagian 9: Board pikeun Board Panyambungna pin ngerjakeun

Inti dewan boga jumlahna aya opat-speed tinggi dewan panyambungna dewan.

Dewan inti ngagunakeun opat 80-pin panyambungna antar-dewan pikeun nyambung ka dewan pamawa. Port IO tina FPGA disambungkeun ka opat panyambungna ku routing diferensial. Jarak pin panyambungna nyaéta 0.5mm, selapkeun kana papan kana konektor papan dina papan pamawa pikeun komunikasi data anu gancang.

Dewan pikeun Board Panyambungna CON1

Papan 80-pin ka konektor dewan CON1, nu dipaké pikeun nyambungkeun jeung catu daya VCCIN (+ 5V) jeung taneuh dina dewan pamawa, manjangkeun IOs normal tina FPGA. Ieu kudu dicatet yén 15 pin CON1 disambungkeun ka port IO of BANK34, sabab sambungan BANK34 disambungkeun ka DDR3. Ku alatan éta, voltage standar sadaya IOs BANK34 ieu 1.5V.

Pin Assignment of Board pikeun Board Panyambungna CON1

| CON1 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

CON1 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

| PIN1 | VCCIN | – | +5V | PIN2 | VCCIN | – | +5V |

| PIN3 | VCCIN | – | +5V | PIN4 | VCCIN | – | +5V |

| PIN5 | VCCIN | – | +5V | PIN6 | VCCIN | – | +5V |

| PIN7 | VCCIN | – | +5V | PIN8 | VCCIN | – | +5V |

| PIN9 | GND | – | taneuh | PIN10 | GND | – | taneuh |

| PIN11 | NC | – | NC | PIN12 | NC | – | NC |

| PIN13 | NC | – | NC | PIN14 | NC | – | NC |

| PIN15 | NC | – | NC | PIN16 | B13_L4_P | AA15 | 3.3V |

| PIN17 | NC | – | NC | PIN18 | B13_L4_N | AB15 | 3.3V |

| PIN19 | GND | – | taneuh | PIN20 | GND | – | taneuh |

| PIN21 | B13_L5_P | Y13 | 3.3V | PIN22 | B13_L1_P | Y16 | 3.3V |

| PIN23 | B13_L5_N | AA14 | 3.3V | PIN24 | B13_L1_N | AA16 | 3.3V |

| PIN25 | B13_L7_P | AB11 | 3.3V | PIN26 | B13_L2_P | AB16 | 3.3V |

| PIN27 | B13_L7_P | AB12 | 3.3V | PIN28 | B13_L2_N | AB17 | 3.3V |

| PIN29 | GND | – | taneuh | PIN30 | GND | – | taneuh |

| PIN31 | B13_L3_P | AA13 | 3.3V | PIN32 | B13_L6_P | W14 | 3.3V |

| PIN33 | B13_L3_N | AB13 | 3.3V | PIN34 | B13_L6_N | Y14 | 3.3V |

| PIN35 | B34_L23_P | Y8 | 1.5V | PIN36 | B34_L20_P | AB7 | 1.5V |

| PIN37 | B34_L23_N | Y7 | 1.5V | PIN38 | B34_L20_N | AB6 | 1.5V |

| PIN39 | GND | – | taneuh | PIN40 | GND | – | taneuh |

| PIN41 | B34_L18_N | AA6 | 1.5V | PIN42 | B34_L21_N | V8 | 1.5V |

| PIN43 | B34_L18_P | Y6 | 1.5V | PIN44 | B34_L21_P | V9 | 1.5V |

| PIN45 | B34_L19_P | V7 | 1.5V | PIN46 | B34_L22_P | AA8 | 1.5V |

| PIN47 | B34_L19_N | W7 | 1.5V | PIN48 | B34_L22_N | AB8 | 1.5V |

| PIN49 | GND | – | taneuh | PIN50 | GND | – | taneuh |

| PIN51 | XADC_VN | M9 | Analog | PIN52 | NC | ||

| PIN53 | XADC_VP | L10 | Analog | PIN54 | B34_L25 | U7 | 1.5V |

| PIN55 | NC | – | NC | PIN56 | B34_L24_P | W9 | 1.5V |

| PIN57 | NC | – | NC | PIN58 | B34_L24_N | Y9 | 1.5V |

| PIN59 | GND | – | taneuh | PIN60 | GND | – | taneuh |

| PIN61 | B16_L1_N | F14 | 3.3V | PIN62 | NC | – | NC |

| PIN63 | B16_L1_P | F13 | 3.3V | PIN64 | NC | – | NC |

| PIN65 | B16_L4_N | E14 | 3.3V | PIN66 | NC | – | NC |

| PIN67 | B16_L4_P | E13 | 3.3V | PIN68 | NC | – | NC |

| PIN69 | GND | – | taneuh | PIN70 | GND | – | taneuh |

| PIN71 | B16_L6_N | D15 | 3.3V | PIN72 | NC | – | NC |

| PIN73 | B16_L6_P | D14 | 3.3V | PIN74 | NC | – | NC |

| PIN75 | B16_L8_P | C13 | 3.3V | PIN76 | NC | – | NC |

| PIN77 | B16_L8_N | B13 | 3.3V | PIN78 | NC | – | NC |

| PIN79 | NC | – | NC | PIN80 | NC | – | NC |

angka 9-1: Board pikeun Board Panyambungna CON1 on Board Core

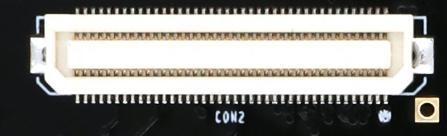

Dewan pikeun Board Panyambungna CON2

80-pin bikang sambungan lulugu CON2 dipaké pikeun manjangkeun IO normal tina BANK13 na BANK14 tina FPGA. voltage standar duanana BANK nyaeta 3.3V.

Pin Assignment of Board pikeun Board Panyambungna CON2

| CON2 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

CON2 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

| PIN1 | B13_L16_P | W15 | 3.3V | PIN2 | B14_L16_P | V17 | 3.3V |

| PIN3 | B13_L16_N | W16 | 3.3V | PIN4 | B14_L16_N | W17 | 3.3V |

| PIN5 | B13_L15_P | T14 | 3.3V | PIN6 | B13_L14_P | U15 | 3.3V |

| PIN7 | B13_L15_N | T15 | 3.3V | PIN8 | B13_L14_N | V15 | 3.3V |

| PIN9 | GND | – | taneuh | PIN10 | GND | – | taneuh |

| PIN11 | B13_L13_P | V13 | 3.3V | PIN12 | B14_L10_P | AB21 | 3.3V |

| PIN13 | B13_L13_N | V14 | 3.3V | PIN14 | B14_L10_N | AB22 | 3.3V |

| PIN15 | B13_L12_P | W11 | 3.3V | PIN16 | B14_L8_N | AA21 | 3.3V |

| PIN17 | B13_L12_N | W12 | 3.3V | PIN18 | B14_L8_P | AA20 | 3.3V |

| PIN19 | GND | – | taneuh | PIN20 | GND | – | taneuh |

| PIN21 | B13_L11_P | Y11 | 3.3V | PIN22 | B14_L15_N | AB20 | 3.3V |

| PIN23 | B13_L11_N | Y12 | 3.3V | PIN24 | B14_L15_P | AA19 | 3.3V |

| PIN25 | B13_L10_P | V10 | 3.3V | PIN26 | B14_L17_P | AA18 | 3.3V |

| PIN27 | B13_L10_N | W10 | 3.3V | PIN28 | B14_L17_N | AB18 | 3.3V |

| PIN29 | GND | – | taneuh | PIN30 | GND | – | taneuh |

| PIN31 | B13_L9_N | AA11 | 3.3V | PIN32 | B14_L6_N | T20 | 3.3V |

| PIN33 | B13_L9_P | AA10 | 3.3V | PIN34 | B13_IO0 | Y17 | 3.3V |

| PIN35 | B13_L8_N | AB10 | 3.3V | PIN36 | B14_L7_N | W22 | 3.3V |

| PIN37 | B13_L8_P | AA9 | 3.3V | PIN38 | B14_L7_P | W21 | 3.3V |

| PIN39 | GND | – | taneuh | PIN40 | GND | – | taneuh |

| PIN41 | B14_L11_N | V20 | 3.3V | PIN42 | B14_L4_P | T21 | 3.3V |

| PIN43 | B14_L11_P | U20 | 3.3V | PIN44 | B14_L4_N | U21 | 3.3V |

| PIN45 | B14_L14_N | V19 | 3.3V | PIN46 | B14_L9_P | Y21 | 3.3V |

| PIN47 | B14_L14_P | V18 | 3.3V | PIN48 | B14_L9_N | Y22 | 3.3V |

| PIN49 | GND | – | taneuh | PIN50 | GND | – | taneuh |

| PIN51 | B14_L5_N | R19 | 3.3V | PIN52 | B14_L12_N | W20 | 3.3V |

| PIN53 | B14_L5_P | P19 | 3.3V | PIN54 | B14_L12_P | W19 | 3.3V |

| PIN55 | B14_L18_N | U18 | 3.3V | PIN56 | B14_L13_N | Y19 | 3.3V |

| PIN57 | B14_L18_P | U17 | 3.3V | PIN58 | B14_L13_P | Y18 | 3.3V |

| PIN59 | GND | – | taneuh | PIN60 | GND | – | taneuh |

| PIN61 | B13_L17_P | T16 | 3.3V | PIN62 | B14_L3_N | V22 | 3.3V |

| PIN63 | B13_L17_N | U16 | 3.3V | PIN64 | B14_L3_P | U22 | 3.3V |

| PIN65 | B14_L21_N | P17 | 3.3V | PIN66 | B14_L20_N | T18 | 3.3V |

| PIN67 | B14_L21_P | N17 | 3.3V | PIN68 | B14_L20_P | R18 | 3.3V |

| PIN69 | GND | – | taneuh | PIN70 | GND | – | taneuh |

| PIN71 | B14_L22_P | P15 | 3.3V | PIN72 | B14_L19_N | R14 | 3.3V |

| PIN73 | B14_L22_N | R16 | 3.3V | PIN74 | B14_L19_P | P14 | 3.3V |

| PIN75 | B14_L24_N | R17 | 3.3V | PIN76 | B14_L23_P | N13 | 3.3V |

| PIN77 | B14_L24_P | P16 | 3.3V | PIN78 | B14_L23_N | N14 | 3.3V |

| PIN79 | B14_IO0 | P20 | 3.3V | PIN80 | B14_IO25 | N15 | 3.3V |

angka 9-2: Board pikeun Board Panyambungna CON2 on Board Core

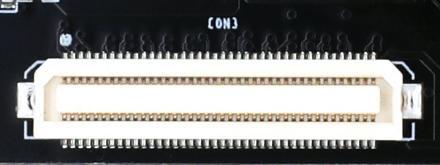

Dewan pikeun Board Panyambungna CON3

80-pin konektor CON3 dipaké pikeun manjangkeun IO normal tina BANK15 jeung BANK16 tina FPGA. Sajaba ti éta, opat JTAG sinyal ogé disambungkeun ka dewan pamawa via konektor CON3. voltage standar BANK15 na BANK16 bisa disaluyukeun ku chip LDO. LDO dipasang standar nyaéta 3.3V. Upami anjeun hoyong kaluaran tingkat standar anu sanés, anjeun tiasa ngagentos éta ku LDO anu cocog.

Pin Assignment of Board pikeun Board Panyambungna CON3

| CON3 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

CON3 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

| PIN1 | B15_IO0 | J16 | 3.3V | PIN2 | B15_IO25 | M17 | 3.3V |

| PIN3 | B16_IO0 | F15 | 3.3V | PIN4 | B16_IO25 | F21 | 3.3V |

| PIN5 | B15_L4_P | G17 | 3.3V | PIN6 | B16_L21_N | A21 | 3.3V |

| PIN7 | B15_L4_N | G18 | 3.3V | PIN8 | B16_L21_P | B21 | 3.3V |

| PIN9 | GND | – | taneuh | PIN10 | GND | – | taneuh |

| PIN11 | B15_L2_P | G15 | 3.3V | PIN12 | B16_L23_P | E21 | 3.3V |

| PIN13 | B15_L2_N | G16 | 3.3V | PIN14 | B16_L23_N | D21 | 3.3V |

| PIN15 | B15_L12_P | J19 | 3.3V | PIN16 | B16_L22_P | E22 | 3.3V |

| PIN17 | B15_L12_N | H19 | 3.3V | PIN18 | B16_L22_N | D22 | 3.3V |

| PIN19 | GND | – | taneuh | PIN20 | GND | – | taneuh |

| PIN21 | B15_L11_P | J20 | 3.3V | PIN22 | B16_L24_P | G21 | 3.3V |

| PIN23 | B15_L11_N | J21 | 3.3V | PIN24 | B16_L24_N | G22 | 3.3V |

| PIN25 | B15_L1_N | G13 | 3.3V | PIN26 | B15_L8_N | G20 | 3.3V |

| PIN27 | B15_L1_P | H13 | 3.3V | PIN28 | B15_L8_P | H20 | 3.3V |

| PIN29 | GND | – | taneuh | PIN30 | GND | – | taneuh |

| PIN31 | B15_L5_P | J15 | 3.3V | PIN32 | B15_L7_N | H22 | 3.3V |

| PIN33 | B15_L5_N | H15 | 3.3V | PIN34 | B15_L7_P | J22 | 3.3V |

| PIN35 | B15_L3_N | H14 | 3.3V | PIN36 | B15_L9_P | K21 | 3.3V |

| PIN37 | B15_L3_P | J14 | 3.3V | PIN38 | B15_L9_N | K22 | 3.3V |

| PIN39 | GND | – | taneuh | PIN40 | GND | – | taneuh |

| PIN41 | B15_L19_P | K13 | 3.3V | PIN42 | B15_L15_N | M22 | 3.3V |

| PIN43 | B15_L19_N | K14 | 3.3V | PIN44 | B15_L15_P | N22 | 3.3V |

| PIN45 | B15_L20_P | M13 | 3.3V | PIN46 | B15_L6_N | H18 | 3.3V |

| PIN47 | B15_L20_N | L13 | 3.3V | PIN48 | B15_L6_P | H17 | 3.3V |

| PIN49 | GND | – | taneuh | PIN50 | GND | – | taneuh |

| PIN51 | B15_L14_P | L19 | 3.3V | PIN52 | B15_L13_N | K19 | 3.3V |

| PIN53 | B15_L14_N | L20 | 3.3V | PIN54 | B15_L13_P | K18 | 3.3V |

| PIN55 | B15_L21_P | K17 | 3.3V | PIN56 | B15_L10_P | M21 | 3.3V |

| PIN57 | B15_L21_N | J17 | 3.3V | PIN58 | B15_L10_N | L21 | 3.3V |

| PIN59 | GND | – | taneuh | PIN60 | GND | – | taneuh |

| PIN61 | B15_L23_P | L16 | 3.3V | PIN62 | B15_L18_P | N20 | 3.3V |

| PIN63 | B15_L23_N | K16 | 3.3V | PIN64 | B15_L18_N | M20 | 3.3V |

| PIN65 | B15_L22_P | L14 | 3.3V | PIN66 | B15_L17_N | N19 | 3.3V |

| PIN67 | B15_L22_N | L15 | 3.3V | PIN68 | B15_L17_P | N18 | 3.3V |

| PIN69 | GND | – | taneuh | PIN70 | GND | – | taneuh |

| PIN71 | B15_L24_P | M15 | 3.3V | PIN72 | B15_L16_P | M18 | 3.3V |

| PIN73 | B15_L24_N | M16 | 3.3V | PIN74 | B15_L16_N | L18 | 3.3V |

| PIN75 | NC | – | PIN76 | NC | – | ||

| PIN77 | FPGA_TCK | V12 | 3.3V | PIN78 | FPGA_TDI | R13 | 3.3V |

| PIN79 | FPGA_TDO | U13 | 3.3V | PIN80 | FPGA_TMS | T13 | 3.3V |

angka 9-3: Board pikeun Board Panyambungna CON3 on Board Core

Dewan pikeun Board Panyambungna CON4

80-Pin konektor CON4 dipaké pikeun manjangkeun IO na GTP normal data-speed tinggi jeung sinyal jam tina FPGA BANK16. voltage standar port IO of BANK16 bisa disaluyukeun ku chip LDO. LDO dipasang standar nyaéta 3.3V. Upami pangguna hoyong kaluaran tingkat standar anu sanés, éta tiasa diganti ku LDO anu cocog. Data-speed tinggi jeung sinyal jam tina GTP anu ketat diferensial routed dina dewan inti. Garis datana sarua panjangna sarta dijaga dina interval nu tangtu pikeun nyegah gangguan sinyal.

Pin Assignment of Board pikeun Board Panyambungna CON4

| CON4 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

CON4 PIN |

Net Ngaran |

FPGA PIN |

Voltage Tingkat |

| PIN1 | NC | – | – | PIN2 | – | – | |

| PIN3 | NC | – | – | PIN4 | – | – | |

| PIN5 | NC | – | – | PIN6 | – | – | |

| PIN7 | NC | – | – | PIN8 | – | – | |

| PIN9 | GND | – | taneuh | PIN10 | GND | – | taneuh |

| PIN11 | NC | – | – | PIN12 | MGT_TX2_P | B6 | Béda |

| PIN13 | NC | – | – | PIN14 | MGT_TX2_N | A6 | Béda |

| PIN15 | GND | – | taneuh | PIN16 | GND | – | taneuh |

| PIN17 | MGT_TX3_P | D7 | Béda | PIN18 | MGT_RX2_P | B10 | Béda |

| PIN19 | MGT_TX3_N | C7 | Béda | PIN20 | MGT_RX2_N | A10 | Béda |

| PIN21 | GND | – | taneuh | PIN22 | GND | – | taneuh |

| PIN23 | MGT_RX3_P | D9 | Béda | PIN24 | MGT_TX0_P | B4 | Béda |

| PIN25 | MGT_RX3_N | C9 | Béda | PIN26 | MGT_TX0_N | A4 | Béda |

| PIN27 | GND | – | taneuh | PIN28 | GND | – | taneuh |

| PIN29 | MGT_TX1_P | D5 | Béda | PIN30 | MGT_RX0_P | B8 | Béda |

| PIN31 | MGT_TX1_N | C5 | Béda | PIN32 | MGT_RX0_N | A8 | Béda |

| PIN33 | GND | – | taneuh | PIN34 | GND | – | taneuh |

| PIN35 | MGT_RX1_P | D11 | Béda | PIN36 | MGT_CLK1_P | F10 | Béda |

| PIN37 | MGT_RX1_N | C11 | Béda | PIN38 | MGT_CLK1_N | E10 | Béda |

| PIN39 | GND | – | taneuh | PIN40 | GND | – | taneuh |

| PIN41 | B16_L5_P | E16 | 3.3V | PIN42 | B16_L2_P | F16 | 3.3V |

| PIN43 | B16_L5_N | D16 | 3.3V | PIN44 | B16_L2_N | E17 | 3.3V |

| PIN45 | B16_L7_P | B15 | 3.3V | PIN46 | B16_L3_P | C14 | 3.3V |

| PIN47 | B16_L7_N | B16 | 3.3V | PIN48 | B16_L3_N | C15 | 3.3V |

| PIN49 | GND | – | taneuh | PIN50 | GND | – | taneuh |

| PIN51 | B16_L9_P | A15 | 3.3V | PIN52 | B16_L10_P | A13 | 3.3V |

| PIN53 | B16_L9_N | A16 | 3.3V | PIN54 | B16_L10_N | A14 | 3.3V |

| PIN55 | B16_L11_P | B17 | 3.3V | PIN56 | B16_L12_P | D17 | 3.3V |

| PIN57 | B16_L11_N | B18 | 3.3V | PIN58 | B16_L12_N | C17 | 3.3V |

| PIN59 | GND | – | taneuh | PIN60 | GND | – | taneuh |

| PIN61 | B16_L13_P | C18 | 3.3V | PIN62 | B16_L14_P | E19 | 3.3V |

| PIN63 | B16_L13_N | C19 | 3.3V | PIN64 | B16_L14_N | D19 | 3.3V |

| PIN65 | B16_L15_P | F18 | 3.3V | PIN66 | B16_L16_P | B20 | 3.3V |

| PIN67 | B16_L15_N | E18 | 3.3V | PIN68 | B16_L16_N | A20 | 3.3V |

| PIN69 | GND | – | taneuh | PIN70 | GND | – | taneuh |

| PIN71 | B16_L17_P | A18 | 3.3V | PIN72 | B16_L18_P | F19 | 3.3V |

| PIN73 | B16_L17_N | A19 | 3.3V | PIN74 | B16_L18_N | F20 | 3.3V |

| PIN75 | B16_L19_P | D20 | 3.3V | PIN76 | B16_L20_P | C22 | 3.3V |

| PIN77 | B16_L19_N | C20 | 3.3V | PIN78 | B16_L20_N | B22 | 3.3V |

| PIN79 | NC | – | PIN80 | NC | – |

angka 9-4: Board pikeun Board Panyambungna CON4 on Board Core

Bagian 10: suplai kakuatan

The AC7A200 FPGA core dewan ieu Powered by DC5V via carrier board, sarta ieu Powered by Mini USB panganteur lamun dipaké nyalira. Kade ulah nyadiakeun kakuatan ku Mini USB jeung dewan pamawa dina waktos anu sareng pikeun nyegah karuksakan. Diagram desain catu daya dina dewan dipidangkeun dina Gambar 10-1.

Gambar 10-1: Catu daya dina skématik papan inti

Dewan inti ieu Powered by + 5V sarta dirobah jadi + 3.3V, + 1.5V, + 1.8V, + 1.0V suplai kakuatan opat arah ngaliwatan tilu DC / DC catu daya chip TLV62130RGT. Arus +1.0V tiasa dugi ka 6A, sareng tilu arus kaluaran sanésna tiasa dugi ka 3A. VCCIO dihasilkeun ku hiji LDOSPX3819M5-3-3. VCCIO utamina nyayogikeun kakuatan ka BANK15 sareng BANK16 FPGA. Pamaké bisa ngarobah IO of BANK15,16 mun vol bédatage standar ku ngaganti chip LDO maranéhna. 1.5V ngahasilkeun VTT sareng VREF voltages diperlukeun ku DDR3 via TPS51200 TI urang. Catu daya 1.8V MGTAVTT sareng MGTAVCC pikeun transceiver GTP dihasilkeun ku chip TPS74801 TI. Fungsi unggal distribusi daya dipidangkeun dina tabel ieu:

| Sasayogian tanaga | Fungsi |

| +1.0V | Inti FPGA Voltage |

| +1.8V | FPGA bantu voltage, TPS74801 catu daya |

| +3.3V | VCCIO of Bank0, Bank13 jeung Bank14 of FPGA, QSIP FLASH, Jam Kristal |

| +1.5V | DDR3, Bank34 jeung Bank35 of FPGA |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA Bank15, Bank16 |

| MGTAVTT(+1.2V) | GTP Transceiver Bank216 of FPGA |

| MGTVCC(+1.0V) | GTP Transceiver Bank216 of FPGA |

Kusabab catu daya Artix-7 FPGA ngagaduhan sarat urutan kakuatan, dina desain sirkuit, kami parantos ngararancang dumasar kana syarat kakuatan chip, sareng kakuatan-on nyaéta 1.0V->1.8V->(1.5). V, 3.3V, VCCIO) jeung 1.0V-> MGTAVCC -> MGTAVTT, desain sirkuit pikeun mastikeun operasi normal tina chip.

Sirkuit kakuatan dina papan inti AC7A200 FPGA dipidangkeun dina Gambar 10-2:

angka 10-2: Power Supply dina AC7A200 FPGA Core Board

Bagian 11: Ukuran Diménsi

Angka 11-1: Papan Inti AC7A200 FPGA (Top View)

Angka 11-2: Papan Inti AC7A200 FPGA (Bottom View)

Dokumén / Sumberdaya

|

ALINX AC7A200 ARTIX-7 FPGA Development Board [pdf] Manual pamaké AC7A200 ARTIX-7 FPGA Development Board, AC7A200, ARTIX-7 FPGA Development Board, FPGA Development Board, Development Board, Board |