intel High-Level Synthesis Compiler Pro Edition

Émbaran produk

| Ngaran produk | Intel High-Level Synthesis Compiler Pro Edition |

|---|---|

| Vérsi | 22.4 |

| Tanggal paleupasan | 19 Désémber 2022 |

| Bewara Deprecation | Intel High-Level Synthesis Compiler direncanakeun janten deprecated sanggeus Vérsi 23.4. |

Parentah Pamakéan Produk

Ngamimitian Guide

- Initialize lingkungan kompiler Anjeun.

- Review rupa-rupa desain examples jeung tutorials disadiakeun kalawan Intel HLS kompiler.

Guide pamaké

- Pituduh Pamaké nyadiakeun pitunjuk ngeunaan

- Sintésis, verifikasi, sareng simulasi hak cipta intelektual (IP) anu dirancang pikeun produk Intel FPGA.

- Ngaliwatan sakabéh aliran ngembangkeun komponén anjeun ti nyieun komponén anjeun sarta testbench nepi ka ngahijikeun IP komponén anjeun kana sistem nu leuwih gede jeung software Intel Quartus Prime.

Guide Praktek pangalusna

Pituduh Praktek Pangsaéna nyayogikeun téknik sareng prakték anu anjeun tiasa nerapkeun pikeun ningkatkeun pamanfaatan daérah FPGA sareng kinerja komponén HLS anjeun. Larapkeun prakték pangsaéna ieu saatos marios kabeneran fungsional komponén anjeun.

Manual Rujukan

Reference Manual nyadiakeun émbaran rujukan ngeunaan fitur nu dirojong ku Intel HLS Compiler. Panggihan rinci ngeunaan pilihan paréntah Intel HLS Compiler, lulugu files, pragmas, atribut, makro, deklarasi, argumen, jeung perpustakaan template.

Intel® High Level Synthesis Compiler Pro Edition Vérsi 22.4 Catetan Release

- Intel® High Level Synthesis Compiler Pro Edition Release Notes nyadiakeun inpo telat-telat ngeunaan Intel High Level Synthesis Compiler Pro Edition Vérsi 22.4.

Nungguan Deprecation tina Intel HLS Compiler

- Pikeun tetep aksés ka fitur desain tingkat luhur FPGA panganyarna, optimasi, sareng utilitas pamekaran, migrasikeun desain anjeun anu tos aya pikeun nganggo Intel oneAPI Base Toolkit.

- Kompiler Intel High Level Synthesis (HLS) direncanakeun bakal dileungitkeun saatos Vérsi 23.4.

- Tingali halaman produk Intel oneAPI pikeun naséhat migrasi, atanapi angkat ka forum komunitas Intel High Level Design pikeun patarosan atanapi pamundut.

Ngeunaan Perpustakaan Dokuméntasi Intel HLS Compiler Pro Edition

- Dokuméntasi pikeun Intel HLS Compiler Pro Edition dibagi kana sababaraha publikasi. Anggo tabel di handap ieu pikeun milarian publikasi anu ngandung inpormasi Intel HLS Compiler Pro Edition anu anjeun milarian:

Tabél 1. Intel High-Level Synthesis Compiler Pro Edition Dokuméntasi Perpustakaan

| Judul sareng Pedaran | |

| Catetan Kaluaran

Nyadiakeun informasi telat-megatkeun ngeunaan Intel HLS Compiler. |

Tumbu |

| Ngamimitian Guide

Bangun sareng ngajalankeun sareng Intel HLS Compiler ku diajar kumaha cara ngamimitian lingkungan kompiler sareng ulangviewdina rupa-rupa desain examples jeung tutorials disadiakeun kalawan Intel HLS kompiler. |

Tumbu |

| Guide pamaké

Nyadiakeun parentah pikeun nyintésis, verifikasi, jeung simulasi hak cipta intelektual (IP) nu Anjeun rancang pikeun produk Intel FPGA. Ngaliwatan sakabéh aliran ngembangkeun komponén anjeun ti nyieun komponén anjeun sarta testbench nepi ka ngahijikeun IP komponén anjeun kana sistem nu leuwih gede jeung software Intel Quartus Prime. |

Tumbu |

| Guide Praktek pangalusna

Nyayogikeun téknik sareng prakték anu anjeun tiasa nerapkeun pikeun ningkatkeun pamanfaatan daérah FPGA sareng kinerja komponén HLS anjeun. Biasana, anjeun nerapkeun prakték pangsaéna ieu saatos anjeun pariksa kabeneran fungsional komponén anjeun. |

Tumbu |

| Manual Rujukan

Nyadiakeun inpormasi rujukan ngeunaan fitur anu dirojong ku Intel HLS Compiler. Panggihan rinci ngeunaan pilihan paréntah Intel HLS Compiler, lulugu files, pragmas, atribut, makro, deklarasi, argumen, jeung perpustakaan template. |

Tumbu |

Intel Corporation. Sadaya hak disimpen. Intel, logo Intel, sareng merek Intel sanés mangrupikeun mérek dagang Intel Corporation atanapi anak perusahaanna. Intel ngajamin kinerja produk FPGA sareng semikonduktor na kana spésifikasi ayeuna saluyu sareng garansi standar Intel, tapi ngagaduhan hak pikeun ngarobih naon waé produk sareng jasa iraha waé tanpa aya bewara. Intel henteu nanggung tanggung jawab atanapi tanggung jawab anu timbul tina aplikasi atanapi pamakean inpormasi, produk, atanapi jasa anu dijelaskeun di dieu iwal ti dinyatakeun sapuk sacara tinulis ku Intel. Konsumén Intel disarankan pikeun ménta versi panganyarna tina spésifikasi alat sateuacan ngandelkeun inpormasi anu diterbitkeun sareng sateuacan nempatkeun pesenan produk atanapi jasa.

*Ngaran sareng merek sanésna tiasa diklaim salaku hak milik batur.

Nungguan Deprecation tina Intel HLS Compiler

- Pikeun tetep aksés ka fitur desain tingkat luhur FPGA panganyarna, optimasi, sareng utilitas pamekaran, migrasikeun desain anjeun anu tos aya pikeun nganggo Intel oneAPI Base Toolkit.

- Kompiler Intel High Level Synthesis (HLS) direncanakeun bakal dileungitkeun saatos Vérsi 23.4.

- Tingali halaman produk Intel oneAPI pikeun naséhat migrasi, atanapi angkat ka forum komunitas Intel High Level Design pikeun patarosan atanapi pamundut.

Fitur anyar jeung Enhancements

- Intel High Level Synthesis Compiler Pro Edition Version 22.4 ngawengku fitur-fitur anyar ieu:

- release pangropéa.

- Taya fitur anyar atawa perbaikan pikeun Intel HLS Compiler Pro Edition Vérsi 22.4.

Parobahan dina Paripolah Software

- Bagian ieu ngadokuméntasikeun instansi dimana fitur Intel HLS Compiler Pro Edition Vérsi 22.4 parantos robih tina sékrési kompiler sateuacana.

release pangropéa.

- Taya parobahan kabiasaan software pikeun Intel HLS Compiler Pro Edition Vérsi 22.4.

Intel High-Level Synthesis Compiler Pro Edition Prasyarat

- Intel HLS Compiler Pro Edition mangrupikeun bagian tina Intel Quartus® Prime Pro Edition Design Suite. Anjeun tiasa masang Intel HLS Compiler salaku bagian tina pamasangan software Intel Quartus Prime anjeun atanapi pasang nyalira. Merlukeun Intel Quartus Prime jeung software tambahan ngagunakeun.

- Pikeun parentah lengkep ihwal masang software Intel Quartus Prime Pro Edition, kaasup sarat sistem, prasyarat, jeung sarat lisénsi, tingali Intel FPGA Software Instalasi jeung Lisensi.

- Intel HLS Compiler merlukeun parangkat lunak ieu salian ti Intel Quartus Prime:

C++ Compiler

- Dina Linux, Intel HLS Compiler merlukeun GCC 9.3.0 kaasup perpustakaan GNU C++ jeung utilitas binér (binutils).

- Vérsi GCC ieu disayogikeun salaku bagian tina pamasangan Intel HLS Compiler anjeun. Saatos masang Intel HLS Compiler, GCC 9.3.0 sayogi di /gcc.

- penting: Intel HLS Compiler ngagunakeun / diréktori gcc salaku diréktori toolchain na. Anggo pamasangan GCC ieu pikeun sadaya karya desain anu aya hubunganana sareng HLS anjeun.

- Pikeun Windows, pasang salah sahiji vérsi Microsoft* Visual Studio* Professional ieu:

- Microsoft Visual Studio 2017 Profesional

- Microsoft Visual Studio 2017 Komunitas

- Pikeun pangrojong C++ 17 anu paling anyar, pastikeun yén anjeun nganggo versi panganyarna tina Visual Studio 2017.

- penting: Parangkat lunak Intel HLS Compiler henteu ngadukung vérsi Microsoft Visual Studio lian ti anu dikhususkeun pikeun édisi parangkat lunak.

Siemens * EDA Questa® Simulasi Software

- Dina sistem Windows sareng RedHat Linux, anjeun tiasa masang parangkat lunak simulasi Questa® tina pamasang parangkat lunak Intel Quartus Prime. Pilihan anu sayogi nyaéta kieu:

- Questa Intel FPGA Edition

- Questa Intel FPGA Starter Edition

- Duanana Questa Intel FPGA Edition sareng Questa Intel FPGA Starter Edition merlukeun lisénsi. Lisensi pikeun Questa Intel FPGA Starter Edition gratis. Pikeun detil, tingal Instalasi sareng Lisénsi Software Intel FPGA.

- Alternatipna, Anjeun bisa make versi dilisensikeun Anjeun sorangan tina Siemens * EDA ModelSim * SE atawa software Siemens EDA Questa Advanced Simulator.

- Dina sistem Linux, Questa - Intel FPGA Edition sareng Questa - Intel FPGA Starter Edition meryogikeun paket alat pangembangan Red Hat*.

- Kanggo inpo tentang sadaya versi software ModelSim na Questa nu software Intel ngarojong, tingal bagian Émbaran Interface EDA dina Software jeung Alat Rojongan Release Catetan pikeun édisi Anjeun Intel Quartus Prime Pro Edition.

Émbaran patali

- Intel High Level Sintésis Compiler Ngamimitian Guide

- Sistem Operasi anu Dirojong

- Syarat Software dina Pamasangan sareng Lisénsi Software Intel FPGA

- Émbaran Antarmuka EDA (Intel Quartus Prime Pro Edition)

Isu dipikawanoh tur Workarounds

- Bagian ieu nyayogikeun inpormasi ngeunaan masalah anu dipikanyaho anu mangaruhan Intel HLS Compiler Pro Edition Vérsi 22.4.

| Katerangan | Solusina |

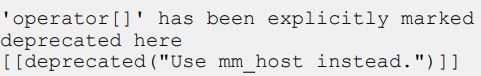

| Nalika anjeun nganggo mm_master kelas deprecated, kompiler ngaluarkeun pesen peringatan sapertos kieu:

Pesen ieu henteu nunjukkeun bagian mana tina kode anjeun anu kedah robih. |

Hindarkeun pesen peringatan ieu ku ngagunakeun kelas mm_host, anu ngagentos kelas mm_master anu dicabut. |

| (Windows wungkul) Nyusun desain dina diréktori kalawan ngaran jalur panjang bisa ngakibatkeun gagal compile.

Pariksa debug.log file pikeun "teu bisa manggihan file” kasalahan. Kasalahan ieu tiasa nunjukkeun yén jalur anjeun panjang teuing. |

Nyusun desain dina diréktori kalayan ngaran jalur pondok. |

| (Windows wungkul) Jalur panjang pikeun diréktori pamasangan Intel Quartus Prime anjeun tiasa nyegah anjeun suksés nyusun sareng ngajalankeun tutorial Intel HLS Compiler sareng mantan.ample desain.

Pariksa debug.log file pikeun "teu bisa manggihan file” kasalahan. Kasalahan ieu tiasa nunjukkeun yén jalur anjeun panjang teuing. |

Pindahkeun tutorials jeung examples kana ngaran jalur pondok sateuacan nyobian ngajalankeun aranjeunna. |

| Katerangan | Solusina |

| Perpustakaan anu nargétkeun OpenCL* sareng ditulis dina HLS teu tiasa nganggo aliran atanapi pipa salaku antarmuka antara kode OpenCL sareng perpustakaan anu ditulis dina HLS.

Tapi, perpustakaan di HLS tiasa nganggo aliran atanapi pipa upami duanana titik tungtung aya dina perpustakaan (pikeun example, aliran anu nyambungkeun dua fungsi tugas). |

N/A |

| Nerapkeun parameter ihc :: maxburst ka panganteur host Avalon® Mémori-Dipetakeun bisa ngabalukarkeun desain Anjeun ngagantung dina simulasi. | N/A |

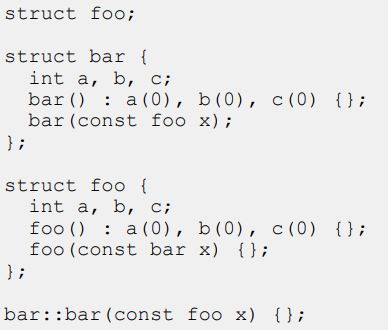

| Dina sababaraha kasus anu jarang, upami anjeun gaduh dua kelas anu konstruktorna masing-masing meryogikeun conto kelas anu sanés salaku input, kompiler tiasa ngadat.

Pikeun example, kompilasi snippet kode ieu nyababkeun kompiler nabrak:

|

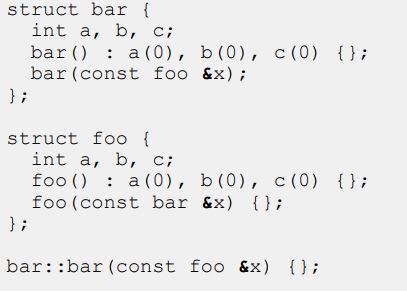

Ulah nyieun harti sirkular. Gantina, make pointer atawa rujukan dina constructor salinan Anjeun.

Pikeun example, transformasi snippet kode saméméhna kana kode handap sarta lulus dina struct salaku rujukan pikeun constructor nu:

|

| Perpustakaan anu nargétkeun OpenCL sareng ditulis dina HLS tiasa nyababkeun kernel OpenCL anu kalebet perpustakaan gaduh kompilasi incremental anu langkung konservatif. | N/A |

| Nalika ngamekarkeun perpustakaan, mun anjeun boga #define ngahartikeun hiji nilai nu Anjeun pake engké di #pragma a, gagal paréntah fpga_crossgen.

Pikeun example, kodeu handap teu bisa disusun ku

|

Anggo pragma tibatan #pragma.

Pikeun example, handap compiles hasil kalawan

|

| Lamun anjeun make pilihan paréntah -c boga kompilasi misah tur linking stages dina workflow Anjeun, sarta lamun teu nangtukeun pilihan -march dina linking stage (atawa tangtukeun nilai pilihan -march béda), linking Anjeun stagtiasa gagal sareng atanapi henteu nganggo pesen kasalahan. | Pastikeun yén anjeun nganggo nilai pilihan -march anu sami pikeun kompilasi sareng pilihan paréntah -c stage jeung linking stage. |

| Katerangan | Solusina |

| Nerapkeun atribut mémori hls_merge kana array anu dinyatakeun dina loop anu henteu digulung atanapi sawaréh henteu digulung nyababkeun salinan arrays tiasa dihijikeun dina iterasi loop anu henteu digulung.

|

Hindarkeun nganggo atribut mémori hls_merge dina puteran anu teu digulung.

Upami anjeun kedah ngahijikeun kenangan dina loop anu teu digulung, sacara eksplisit nyatakeun susunan jinis struktur pikeun ngahijikeun lebar, atanapi nyatakeun susunan anu langkung jero pikeun ngahijikeun jero.

|

| Dina mémori Fungsi Viewer laporan desain tingkat tinggi, sababaraha kenangan fungsi-scoped bisa muncul salaku "dioptimalkeun jauh". | Euweuh.

Nalika a file ngandung fungsi anu komponén jeung fungsi nu teu komponén, kabéh variabel fungsi-scoped dibéréndélkeun di jandela Fungsi Mémori Daptar, tapi ngan variabel ti komponén boga informasi ngeunaan eta pikeun nembongkeun dina Fungsi Mémori. View pane. |

| Sababaraha laporan desain tingkat luhur gagal dina Microsoft Internet Explorer*. | Paké salah sahiji panyungsi handap pikeun view laporan:

• Google Chrome* • Microsoft Edge* • Mozilla* Firefox* |

| The Loop Viewer dina Laporan Desain Tingkat Tinggi ngagaduhan larangan ieu:

• Paripolah klaster lapak-gratis teu dimodelkeun dina Citakan: Loop Vieweh. Latensi ahir anu dipidangkeun dina Loop Viewer pikeun klaster bébas lapak biasana leuwih pesimis (nyaéta, luhur) ti latency sabenerna desain Anjeun. Pikeun pedaran clustering na lapak-gratis klaster, tingal Clustering nu Datapath dina Intel High-Level Synthesis Compiler Pro Edition Guide Praktek Pangalusna. • lapak ti maca jeung nulis ti memori atawa print pernyataan teu dimodelkeun. • itungan High-iteration (> 1000) ngabalukarkeun kinerja slow tina Loop Vieweh. • Anjeun teu bisa nangtukeun hiji count Iteration enol (0) dina Loop Vieweh. |

Euweuh. |

| Tautan dina sababaraha laporan dina Laporan Desain Tingkat Tinggi anu dihasilkeun dina sistem Windows henteu jalan. | Ngahasilkeun Laporan Desain Tingkat Tinggi (nyaéta, kompilasi kode anjeun) dina sistem Linux. |

| Ngagunakeun struct tina tipe data ac_int tunggal dina panganteur steaming anu ngagunakeun pakét (ihc::usesPackets ) teu hasil.

Pikeun example, snippet kode di handap ieu teu jalan:

|

Pikeun ngagunakeun kombinasi ieu dina desain anjeun, taat kana larangan ieu:

• Ukuran data ac_int internal kedah langkung ti 8 • Deklarasi tipe panganteur stream kudu nangtukeun ihc::bitsPerSymbol<8> Pikeun example, snippet kode ieu dianggo:

|

| Katerangan | Solusina | |

| Nalika ngajalankeun simulasi high-throughput komponén anjeun nganggo sauran fungsi enqueue, upami anjeun henteu nganggo fungsi ihc_hls_component_run_all pikeun ngajalankeun sauran komponén anu enqueued saatos sadaya sauran ihc_hls_enqueue pikeun komponén éta, paripolah ieu lumangsung:

• Dina emulation, fungsi komponén enqueued dijalankeun. • Dina simulasi, fungsi komponén enqueued teu dijalankeun, tanpa kasalahan atawa pesen warning disadiakeun. |

Mastikeun yén anjeun ngagunakeun fungsi ihc_hls_component_run_all sanggeus sakabéh ihc_hls_enqueue nelepon pikeun komponén nu ngajalankeun enqueued nelepon fungsi komponén. | |

| Ngajalankeun fungsi tugas sareng ihc::launch_always_run | Pikeun ngahindarkeun optimasi, tambahkeun sakedap(1) | |

| strips jauh atribut optimasi dilarapkeun ka tugas | loop ka fungsi kapangaruhan nerapkeun kontrol pakait | |

| fungsi. | pragma kana while(1) loop tinimbang fungsi. | |

| Dina kode handap example, atribut dilarapkeun ka fungsi teu dipaliré. Laporan Desain Tingkat Tinggi nunjukkeun II tina 1 pikeun tugas ieu tinimbang anu dipénta II tina 4. | Kodeu handap example nunjukkeun kumaha anjeun tiasa nerapkeun parobahan ieu pikeun urut kode baheulaample: | |

|

|

|

| Pikeun Cyclone® V proyék nu ngandung sababaraha komponén HLS, mun anjeun migunakeun i ++ paréntah pikeun compile proyék anjeun ka hardware (i ++ -march = CycloneV), Anjeun bisa nampa kasalahan.

Nalika téks kasalahan béda-béda gumantung kana proyék anjeun, tanda tangan kasalahan mangrupikeun kagagalan kompilasi Intel Quartus Prime kusabab sintaksis Verilog anu goréng. A modul nyoba ngagunakeun fungsi nu kompiler Intel Quartus Perdana teu bisa manggihan. |

Upami anjeun mendakan masalah ieu, pasang unggal komponén HLS dina proyék anu misah. | |

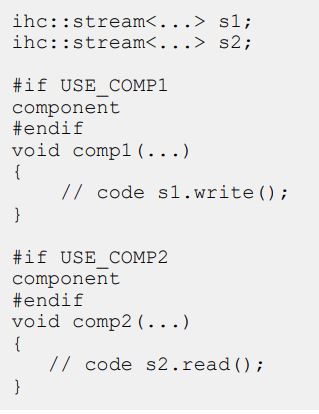

| Nyusun sababaraha desain anu ngandung sababaraha komponén ngahasilkeun kasalahan ngeunaan panggunaan deui aliran. | Upami anjeun mendakan masalah ieu, kompilasi unggal komponén dina desain nyalira. Anjeun panginten kedah nambihan makro kana kode anjeun pikeun ngaktifkeun unggal komponén dikompilasi nyalira. | |

| Pertimbangkeun conto di handap ieuample: | ||

|

||

Intel High-Level Synthesis Compiler Pro Edition Release Notes Archives

Pikeun vérsi panganyarna sareng sateuacana tina pituduh pangguna ieu, tingal Catetan Pelepasan Intel HLS Compiler Pro Edition. Upami vérsi parangkat lunak teu kadaptar, catetan sékrési kanggo vérsi parangkat lunak saacanna dilarapkeun.

Sajarah Révisi Dokumén pikeun Intel HLS Compiler Pro Edition Vérsi 22.4 Catetan Release

| Vérsi Dokumén | Intel Quartus Prime Vérsi | Parobahan |

| 2022.12.19 | 22.4 | • release awal. |

Dokumén / Sumberdaya

|

intel High Level Synthesis Compiler Pro Edition [pdf] Parentah Vérsi 22.4, Vérsi 23.4, High Level Synthesis Compiler Pro Edition, High Level Synthesis Compiler, Pro Edition |