Microsemi RTG4 FPGA Watesan Timing

Émbaran produk

Panungtun Pamaké Watesan Waktu RTG4 FPGA nyayogikeun inpormasi lengkep ngeunaan nerapkeun watesan waktos pikeun objék desain khusus nganggo paréntah SDC. Ieu ngawengku parentah pikeun aksés obyék, spésifikasi obyék eksplisit vs implisit, karakter kartu liar, hirarki sarta separators pin, konvénsi ngaran beus, sarta nambahkeun komentar.

spésifikasi

- Ngaran produk: RTG4 FPGA

- Pituduh pamaké: Timing Konstrain Guide pamaké

Parentah Pamakéan Produk

Aksés Obyék

Pikeun nerapkeun konstrain waktos pikeun ngarancang objék:

- Paké paréntah kawas get_cells, get_clocks, get_nets, get_pins, get_ports, all_inputs, all_outputs, all_registers dumasar kana jenis objék.

- Tingal pitulung online SmartTime pikeun inpo nu leuwih lengkep.

Spésifikasi eksplisit vs implisit

SDC ngarojong spésifikasi obyék implisit sareng eksplisit:

- Spésifikasi implisit nyaéta nalika alat nangtukeun jinis obyék ku milarian obyék.

- Spésifikasi eksplisit ngalibatkeun nangtukeun jenis obyék ngagunakeun paréntah aksés objék nested pikeun ngahindarkeun ambiguitas.

Karakter Kartu liar

Anggo karakter kartu liar dina paréntah SDC:

- (backslash) napsirkeun karakter salajengna sacara harfiah.

- * (asterisk) cocog string mana wae.

Bubuka

Dina ngarancang desain digital sinkron FPGA, ti entri desain nepi ka palaksanaan fisik, jarang anjeun ngahontal kinerja timing diperlukeun tina desain tanpa iteration. Anjeun sering kedah ngaliwat sababaraha iterasi tina siklus desain - néwak desain HDL, sintésis, palaksanaan fisik (Tempat sareng Rute) sareng Analisis Waktu - pikeun ngahontal panutupan waktos. Netepkeun Watesan Timing sareng ngalaksanakeun Analisis Timing mangrupikeun dua léngkah anu paling penting dina iterasi desain nuju panutupan waktos. Pikeun desain RTG4, Microsemi nyarankeun netepkeun konstrain waktos pikeun sintésis sareng tempat sareng léngkah jalur. Anjeun mimitina kudu nyetél konstrain pernyataan timing; tingali "Timing Assertions" dina kaca 5. Lamun kinerja timing teu patepung dina Iteration kahiji, mertimbangkeun nyetel tambahan tur leuwih maju konstrain timing dina iterasi kadua jeung saterusna. Tempo "Pengecualian Timing" dina kaca 6.

Ngagunakeun Synopsys Desain Konstrain

Synopsys® Design Constraint (SDC) mangrupikeun format berbasis Tcl anu dianggo ku alat Synopsys pikeun nangtukeun hajat desain sareng konstrain waktos. Microsemi ngadukung variasi format SDC pikeun manajemén konstrain.

Anjeun tiasa nganggo jinis paréntah SDC ieu nalika nyiptakeun konstrain SDC pikeun desain RTG4:

- Aksés Obyék

- Timing Assertions

- Pangecualian Timing

Aksés Obyék

Konstrain timing SDC dilarapkeun ka objék desain husus. meja 1-1 nyimpulkeun paréntah aksés obyék anu dirojong ku SmartTime (alat analisis timing statik Microsemi anu dilebetkeun sareng alat tempat sareng rute). Tingali kana pitulung online SmartTime kanggo inpormasi lengkep.

Méja 1-1 Paréntah Aksés Obyék Dirojong ku SmartTime

| Objék Desain | Paréntah (s) |

| Sél / Instansi | get_cells |

| Jam | get_clocks |

| Jaring | get_nets |

| Pins | get_pins |

| Palabuhan | get_ports, all_inputs, all_outputs |

| Ngadaptar | sadaya_register |

Spésifikasi implisit vs eksplisit

Sacara umum, paréntah SDC ngawengku objék desain salaku argumen. SDC ngarojong spésifikasi obyék implisit sareng eksplisit.

Nalika alat nangtukeun jinis obyék ku milarian obyék, éta disebut spésifikasi obyék implisit. Nalika tipe objék dieusian (ngahindarkeun ambiguitas) ngagunakeun paréntah aksés objék nested, disebut spésifikasi objék eksplisit.

Pikeun example: Upami Anjeun gaduh net ngaranna 'my_net1', spésifikasi implisit my_net1 jeung spésifikasi eksplisit nyaéta [get_nets my_net1].

Henteu sakabéh objék desain anu lumaku pikeun sakabéh paréntah SDC. Unggal paréntah SDC nampi sakumpulan objék desain anu tos ditetepkeun salaku argumen. Microsemi nyarankeun yén anjeun nganggo metode spésifikasi objék anu eksplisit pikeun ngahindarkeun ambiguitas ngeunaan jinis obyék. Upami sababaraha jinis obyék dipulangkeun saatos milarian spésifikasi implisit, jinis obyék diprioritaskeun dumasar kana daptar obyék prioritas alat.

Tingali kana pitulung online SmartTime kanggo inpormasi lengkep.

Karakter Kartu liar

meja 1-2 daptar karakter kartu liar sadia pikeun pamakéan dina paréntah SDC.

Méja 1-2 Paréntah Aksés Obyék Dirojong ku SmartTime

| Kartu liar | Fungsi |

| \ | Napsirkeun karakter salajengna sacara harfiah |

| * | Cocog wae string |

Catetan: Fungsi cocog merlukeun anjeun nambahkeun backslash (\) saméméh unggal slash dina ngaran pin bisi slash teu nuduhkeun hirarki dina desain Anjeun.

Hierarki jeung Pin Separators

Parangkat lunak Synplify Pro ingkar kana pamakéan '.' (periode) salaku duanana hirarki sarta separators pin pikeun konstrain timing.

Pikeun example: [get_pins {top_level.blockA.instance123.my_pin}] Pikeun ngarobah separator hirarki tina standar '.' (periode) kana '/' (slash payun), nganggo paréntah: set_hierarchy_separator {/}

Parangkat lunak SmartTime ingkar kana panggunaan '/' salaku pemisah hirarki desain sareng ":" salaku karakter pemisah pin.

Pikeun example: [get_pins {top_level / blockA / instance123: my_pin}] Perhatikeun yén '/' nyaéta pamisah hirarki anu dianggo pikeun nunjukkeun yén 'instance123' aya dina hirarki desain di handap top_level 'blockA. Pamisah pin ":" nangtukeun 'my_pin' dina 'instance123'.

Konvénsi Ngaran Beus

Kabéh beus di SDC file kudu make Verilog-gaya ngaran konvénsi ngaran[indéks].

Pikeun example: [get_ports addr_bus_out [1]] Upami anjeun hoyong nangtukeun konstrain dina sakabéh beus, anjeun tiasa nganggo [get_port addr_bus_out].

Koméntar

Anjeun tiasa nambahkeun komentar ka SDC file ku miheulaan garis koméntar ku tanda pon (#).

# Ieu mangrupikeun garis koméntar

Timing Assertions

Assertions timing dimaksudkeun pikeun moto sarat timing desain Anjeun. Aranjeunna kalebet paréntah SDC di handap ieu:

- Jam Periode / Frékuénsi

- create_clock

- create_generated_clock

- Input / Kaluaran reureuh

- set_input_delay

- set_output_delay

- set_external_check

- set_clock_to_output

- Jam-ka-jam Kateupastian

- set_clock_uncertainty

- Latency Sumber Jam

- set_clock_latency

Tingal "Konstrain Waktos sareng Aliran Desain" dina kaca 7 pikeun paréntah SDC Pernyataan Timing Synplify Pro sareng dukungan SmartTime.

Pangecualian Timing

Anggo pangecualian waktos pikeun ngaidentipikasi jalur desain anu meryogikeun hubungan timing siklus tunggal standar pikeun ditimpa. Paréntah SDC pikeun pengecualian waktos kalebet:

- Jalan palsu

- set_false_path

- Jalur multicycle

- set_multicycle_path

- jalur reureuh maksimum

- set_max_delay

- Jalur reureuh minimum

- set_min_delay

- Busur timing ditumpurkeun

- set_disable_timing

Pangecualian Timing sareng Urutan Precedence

Lamun jalur timing sarua boga leuwih ti hiji konstrain iwal timing, SmartTime ngahargaan konstrain timing kalawan precedence pangluhurna sarta ignores iwal timing séjén nurutkeun urutan precedence ditémbongkeun dina Table 1-3. Synplify Pro ngahargaan konstrain waktos numutkeun Urutan Precedence dina Tabel 1-4.

Méja 1-3 Pangecualian Timing - Urutan Precedence pikeun SmartTime

| Pangecualian Timing | Urutan kautamaan |

| set_disable_timing | 1 |

| set_false_path | 2 |

| set_maximum_delay/set_minimum_delay | 3 |

| set_multicycle_path | 4 |

Méja 1-4 Pangecualian Timing - Urutan Precedence pikeun Synplify Pro

| Pangecualian Timing | Urutan kautamaan |

| set_false_path | 1 |

| set_max_delay / set_min_delay | 2 |

| set_multicycle_path | 3 |

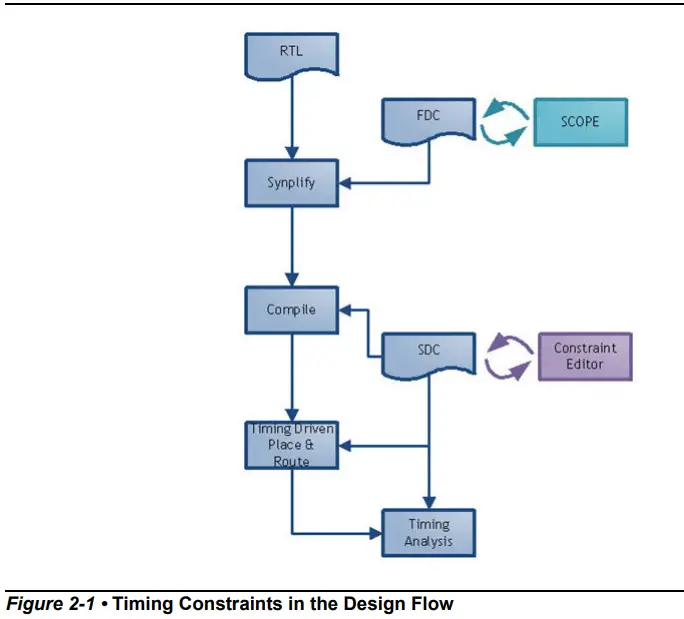

Watesan Timing sareng Aliran Desain

Bab ieu ngajelaskeun dimana nangtukeun konstrain timing sarta ngalakukeun analisis timing dina aliran design Libero (Gambar 2-1). Microsemi nyarankeun yén anjeun nyayogikeun Synplify Pro sareng SmartTime kalayan konstrain waktos anu cekap sareng lengkep. Ogé, anjeun kedah deuiview laporan timing ti duanana Synplify Pro jeung SmartTime pikeun mastikeun yén desain geus konstrain bener jeung keur minuhan tujuan timing.

Alat Libero (Timing Driven Place and Route and SmartTime) ngarojong sawaréh tina Synopsys SDC timing konstrain relevan pikeun desain FPGA.

Microsemi nyarankeun yén anjeun nyiptakeun dua sét konstrain waktos dina aliran Libero:

- Watesan waktos FDC pikeun sintésis sareng Synplify Pro.

- Konstrain timing SDC pikeun Libero Timing Didorong Tempat sareng Rute sareng fase SmartTime.

Watesan waktos pikeun Synplify Pro

- Leuwihview

Synplify Pro ngarojong format FPGA Design Constraints (FDC). Format FDC ngawengku:- A sawaréh ti standar Synopsys SDC pikeun konstrain timing

- Format watesan waktos warisan anu dirojong ku Synplify Pro

Anjeun tiasa nyayogikeun watesan waktos ka Synplify Pro ku: - Ngimpor watesan waktos file(s) kana proyék Libero. Identipikasi konstrain timing file(s) pikeun dibikeun ka Synplify Pro di Libero GUI. Klik katuhu dina file(s) tur pilih Paké pikeun Sintésis. Pikeun detil ngeunaan impor konstrain timing dina Libero GUI, tingal Libero pitulung online.

- Nyiptakeun konstrain waktos nganggo GUI SCOPE (Synthesis Constraints Optimization Environment) anu sayogi dina parangkat lunak Synplify Pro. Konstrain anu diciptakeun nganggo SCOPE disimpen kana konstrain file ngagunakeun format FDC.

- Dirojong Synplify Pro Timing Konstrain

Watesan waktos di handap ieu dirojong ku Synplify Pro pikeun sintésis FPGA:- create_clock

- create_generated_clock

- set_input_delay

- set_output_delay

- set_false_path

- set_multicycle_path

- set_max_delay

- set_clock_latency

- set_clock_uncertainty

Tingal kana Synplify Pro pikeun Microsemi Rujukan Manual pikeun detil ngeunaan pilihan jeung argumen,.

- Watesan pikeun Sarat Desain

Parangkat lunak sintésis ngagunakeun konstrain waktos pikeun ngadamel trade-off anu nyababkeun pamakean sumber daya anu optimal pikeun ngahontal tujuan waktos anu dipénta. Watesan waktos penting pikeun mastikeun yén pilihan anu leres dilakukeun ku alat sintésis nalika ngalaksanakeun logika sareng optimasi pemetaan desain.

Microsemi nyarankeun yén anjeun ngalebetkeun Konstrain Jam sareng Konstrain Tunda Input sareng Output.

Aya dua jinis watesan jam:- create_clock

- create_generated_clock

Pikeun nangtukeun jam desain pikeun desain RTG4,: - Anggo konstrain create_clock pikeun ngaidentipikasi sareng ngawatesan osilator sareng palabuhan input primér anu dianggo salaku jam.

- Paké konstrain create_generated_clock pikeun ngaidentipikasi sarta konstrain pin kaluaran CCC lawon dipaké salaku jam.

- FDC Example kalawan create_clock na create_generated_clock

Dina urutample handap kombinasi create_clock na create_generated_clock konstrain dipaké pikeun nangtukeun konstrain jam diperlukeun.

Kahiji, sumber jam diidentifikasi minangka port input clk_in dina 50 MHz.

Teras sumber jam ieu dianggo pikeun ngahasilkeun jam 200 MHz (clk_core) nganggo CCC:

Catetan: The backslash "\" karakter mangrupa bagian tina sintaksis Tcl. Ngarecah paréntah tunggal panjang kana sababaraha garis.

Catetan: Parangkat lunak Synplify Pro ingkar kana pamakéan '.' (periode) salaku separator hirarki pikeun konstrain timing. Paké paréntah set_hierarchy_separator dina FDC file pikeun ngartikeun ulang karakter pamisah hirarki. Pikeun example:set_hierarchy_separator {/}

Faktor divide_by na multiply_by diturunkeun tina diagram PLL dipintonkeun dina tab 'Advanced' tina configurator CCC lawon. software Synplify Pro ingkar 100 MHz frékuénsi jam diperlukeun pikeun sakabéh jam leungit hiji konstrain timing. - FDC Example kalawan set_input_delay na set_output_delay

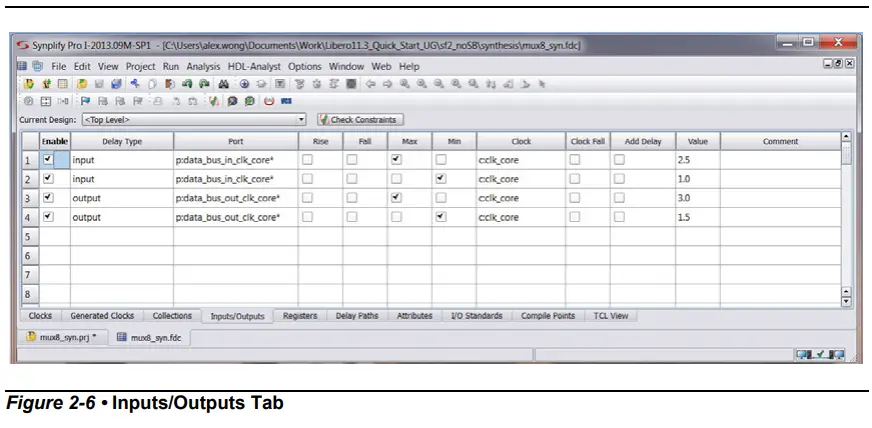

Dina ex ieuample, set_input_delay na set_output_delay konstrain dipaké pikeun nangtukeun input diperlukeun tur kaluaran waktu reureuh konstrain. Konstrain ieu diperlukeun pikeun nangtukeun anggaran timing diperlukeun pikeun Interface I/O.

Dina ex ieuample, sagala konstrain ngagunakeun clk_core ti ex saméméhnaample salaku jam rujukan.

Tunda input dina port input (s) data_bus_in_clk_core nyaeta 2.5ns (max) jeung 1.0ns (mnt).

Kaluaran reureuh dina port kaluaran (s) data_bus_out_clk_core nyaeta 3.0ns (max) jeung 1.5ns (mnt).

# telat input

set_input_delay -jam [get_clocks clk_core] \

-max 2.5 \

[get_ports {data_bus_in_clk_core*}] set_input_delay -clock [get_clocks clk_core] \

-min 1.0 \

[get_ports {data_bus_in_clk_core*}] # kaluaran reureuh

set_output_delay -jam [get_clocks clk_core]\

-max 3.0 \

[get_ports {data_bus_out_clk_core*}] set_output_delay -clock [get_clocks clk_core] \

-min 1.5 \

[meunang_ports {data_bus_out_clk_core*}] - Pamariksaan Konstrain

Microsemi nyarankeun yén anjeun ngesahkeun FDC atanapi konstrain waktos saatos anjeun ngimpor atanapi nyiptakeunana. Ieu hususna penting lamun konstrain timing file diimpor.

Synplify Pro nyadiakeun utilitas checker konstrain nu bisa Anjeun pake pikeun ngesahkeun konstrain SDC timing. Pamariksaan konstrain tiasa diaksés tina ménu proyék (Run> Constraint Check) di jero Synplify Pro GUI. Éta ngahasilkeun laporan cek konstrain (*_cck.rpt) kalayan detil ngeunaan masalah naon waé anu aya watesan waktos. Bagian kasimpulan kedah nunjukkeun yén teu aya masalah anu kapendak sareng konstrain waktos.

Anggo laporan pamariksaan konstrain pikeun ngalereskeun kasalahan anu aya hubunganana sareng sintaksis atanapi nami obyék anu salah.

Pikeun detil ngeunaan Synplify Pro Constraint Checker, tingal Panungtun Pamaké Synplify Pro pikeun Microsemi. - Watesan pikeun Ngaoptimalkeun Desain Anjeun

Sakali konstrain waktos dipariksa, Microsemi nyarankeun yén anjeun nganggo fitur analisis waktos di Synplify Pro pikeun nangtukeun naha sadaya konstrain desain anu diperyogikeun parantos disayogikeun. Anjeun tiasa nganggo daptar jalur desain anu ngalanggar dina laporan waktos pikeun ngaidentipikasi konstrain waktos anu leungit atanapi henteu akurat.

Catetan: Kusabab desain henteu acan disimpen, laporan timing ngagunakeun perkiraan dumasar kana model beban kawat pikeun Nepi net. Ieu alesan yén palanggaran timing di s ieutage tiasa atanapi henteu muncul saatos tempat sareng rute.

Microsemi nyarankeun yén anjeun ngaliwat hiji pass tina sakabéh aliran desain kaasup Timing Driven Place and Route saméméh nambahkeun éntitas timing pikeun sintésis. Anjeun teras tiasa nganggo tempat pos anu langkung akurat sareng laporan analisis timing rute pikeun nangtukeun konstrain anu diperyogikeun.

Watesan Jam, Input sareng Output Delay mangrupikeun set minimum watesan waktos anu diperyogikeun pikeun sadaya desain. Sababaraha desain tiasa meryogikeun konstrain waktos tambahan anu katelah pengecualian waktos. Pikeun example:- Jalur Palsu (set_false_path),

- Jalur Multicycle (set_multicycle_path)

- Tunda Jalur Maksimum (set_max_delay)

Anjeun tiasa nganggo pangecualian waktos pikeun ngaidentipikasi jalur desain anu meryogikeun hubungan timing siklus tunggal standar pikeun ditimpa. Anjeun kedah ngabimbing optimasi alat sintésis ku ngaidentipikasi jalur desain anu: - Henteu gaduh hubungan waktos (set_false_path)

- Boga hubungan timing anu sanés siklus tunggal (set_multicycle_path atanapi set_max_delay)

- Kautamaan

Pikeun ngabéréskeun konflik konstrain waktos nalika sababaraha pangecualian waktos diterapkeun kana objék desain anu sami, aturan precedence di handap ieu diterapkeun:

set_disable_timing diutamakeun tina sagala konstrain pangecualian waktos anu sanés.

Konstrain Jalur Palsu diutamakeun tina Tunda Jalur Maksimum/Tunda Jalur Minimum atanapi Konstrain Jalur Multicycle.

Maksimum Path Reureuh / Minimum Path Reureuh konstrain nyokot precedence leuwih Multicycle Path konstrain.

Méja 2-1 Paréntah Aksés Obyék Dirojong ku SmartTimePangecualian Timing Urutan diutamakeun set_disable_timing 1 set_false_path 2 set_maximum_delay / set_minimum_delay 3 set_multicycle_path 4 - Optimasi pikeun Timing Versus Area

Nalika anjeun ngajalankeun sintésis Synplify Pro, alat mimiti nyusun rarancang teras dipetakeun kana sél téknologi Microsemi.

Sacara standar, Synplify Pro sacara otomatis ngadamel trade-off efisien antara daérah sareng kinerja waktos pikeun ngahontal hasil anu pangsaéna. Nanging, anjeun tiasa ngabimbing Synplify Pro pikeun ngaoptimalkeun desain pikeun pagelaran waktos kalayan biaya daérah. Sabalikna, anjeun tiasa ngabimbing Synplify Pro pikeun ngaoptimalkeun desain pikeun daérah kalayan biaya kinerja waktos.

Sacara umum, ngaoptimalkeun pikeun pagelaran waktos nganggo langkung seueur sumber FPGA (aréa) sareng ngaoptimalkeun pikeun daérah sering hartosna telat anu langkung ageung (kinerja waktos anu langkung lemah). Anjeun kedah nimbangkeun kabutuhan kinerja waktos anjeun sareng kabutuhan daérah anjeun pikeun nangtukeun naon anu paling cocog pikeun desain anjeun.

Tingal Bab 10 tina Synplify Pro pikeun Pituduh Pamaké Microsemi pikeun émbaran nu langkung lengkep ihwal pilihan optimasi. - Analisis Timing Post-Sintésis sareng Synplify Pro

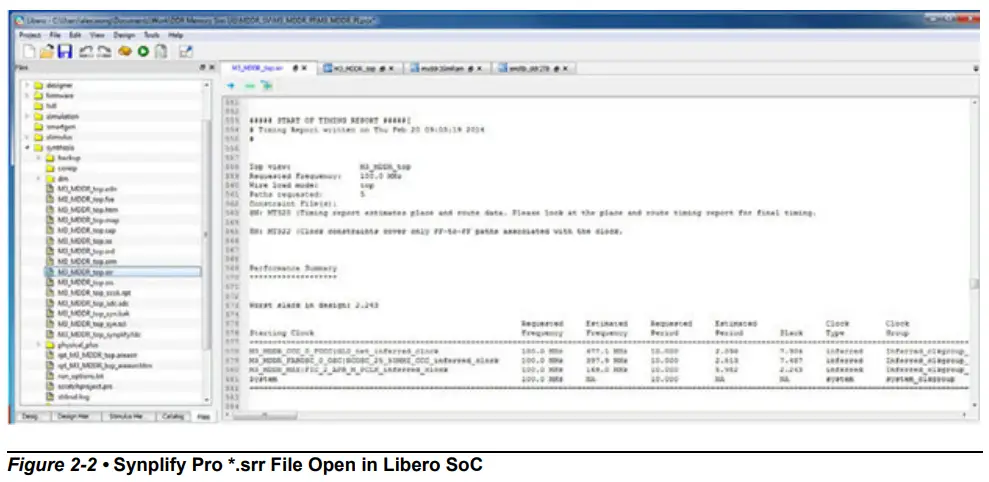

Synplify Pro ngahasilkeun laporan waktos saatos sintésis réngsé. Saatos ngajalankeun sintésis, klik dina View Tombol log pikeun muka log file dina Synplify Pro.

Log sintésis file ogé sayogi ti Libero SoC, dina Synthesize dina panel Reports.

The file lokasina di handapeun diréktori sintésis kalawan * .srr extension na viewtiasa di Libero SoC. Pencét éta File tab dina Proyék Libero SoC anjeun. Ngalegaan Sintésis file grup. Klik dua kali *.srr file pikeun muka éta dina Libero SoC Editor View pane. Gulung ka handap ka bagian anu judulna MULAI LAPORAN WAKTU (Gambar 2-2).

Laporan waktos Synplify Pro dibagi kana bagian-bagian ieu:- Ringkesan Performance

- Jam Hubungan

- Émbaran panganteur

- Laporan lengkep pikeun Jam

Anggo laporan waktos sintésis pikeun mastikeun: - Konstrain keur dipulut jeung diterapkeun saperti nu diharapkeun.

- Desain henteu ngagaduhan palanggaran waktos anu signifikan

Kusabab desain henteu acan disimpen, laporan timing sintésis ngira-ngira telat net ngagunakeun modél beban kawat. Tapi, telat sél anu dianggo dina laporan waktos akurat.

A palanggaran timing setelan bisa dianggap signifikan, lamun reureuh jalur teu kaasup reureuh net ngaleuwihan waktu diperlukeun. Ieu biasana mangrupa indikasi yén boh sarat timing teu realistis atawa jalur desain merlukeun pipelining tambahan. Dina boh kasus, éta pisan saperti teu mirip yén jalur desain jeung reureuh sél ngaleuwihan waktu diperlukeun bakal minuhan tujuan timing sanggeus tempat jeung jalur.

- Pangecualian Timing

Lamun analisis timing pos-sintésis ngalaporkeun yén desain teu minuhan spésifikasi timing pikeun speed jam atawa I / O reureuh, Microsemi nyarankeun yén anjeun ngagunakeun iwal timing pikeun mantuan sintésis.

Microsemi nyarankeun yén anjeun ngaliwat hiji pass tina sakabéh aliran desain, kaasup Timing Driven Place and Route, sateuacan nambihan pengecualian waktos pikeun sintésis. Anjeun teras tiasa nganggo tempat pos anu langkung akurat sareng laporan analisis timing rute pikeun nangtukeun konstrain anu diperyogikeun. Paké konstrain timing jalur palsu pikeun ngaidentipikasi jalur design husus nu teu propagate parobahan tingkat logika jeung teu kudu dianggap salila analisis timing. Alat sintésis teu malire jalur desain anu diidentifikasi nganggo konstrain ieu pikeun logika sareng optimasi pemetaan. Paké Multicycle Path, Path Palsu jeung Maximum Path Reureuh timing konstrain pikeun ngaidentipikasi jalur design nu boga hubungan timing béda ti standar hubungan siklus tunggal. Alat sintésis ngagunakeun hubungan anyar pikeun optimasi.

Konstrain Jalur Multicycle sareng Jalur Palsu biasana nyababkeun sayah sarat waktos siklus jam tunggal asli. Konstrain Path Maksimum Reureuh bisa ngakibatkeun sayah atawa tightening sarat timing aslina dumasar kana nilai waktu dieusian ku pamaké.

FDC Examples

# Jalan Palsu

set_false_path -from [get_ports uart_ctrl] # Tunda Jalur Maksimum

set_max_delay -to [get_ports {ram_rd_enable}] 4.0

# Jalur Multicycle

set_multicycle_path 4 -to [get_ports {I2C*}]

RUANG LINGKUP jeung Ngagunakeun Maju Annotated SDC

Anjeun tiasa nganggo SCOPE ti Synplify Pro pikeun ngasupkeun konstrain pikeun léngkah sintésis. Saatos sintésis, Synplify Pro ngahasilkeun *_sdc.sdc file, nu ngandung wates waktu annotated maju. Tingal "Ngagunakeun SDC Anu Diteruskeun" dina kaca 15 pikeun detil. Aliran anu disarankeun nyaéta nyiptakeun konstrain anu misah pikeun Sintésis sareng léngkah-léngkah Tempat sareng Rute anu Didorong Timing.

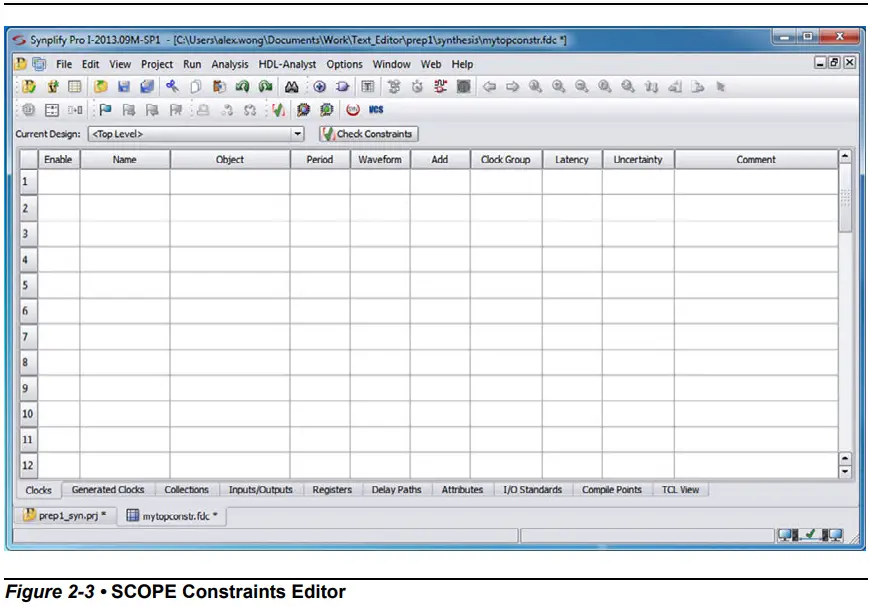

- Timing Konstrain Éntri Ngagunakeun LINGKUP

SCOPE mangrupikeun redaktur anu disayogikeun sareng Synplify Pro pikeun ngalebetkeun sareng ngatur konstrain waktos sareng atribut sintésis (Gambar 2-3).

Tilu jinis konstrain anu umum pikeun kalolobaan desain nyaéta:- Watesan Jam - Sadaya desain sinkron didorong ku sababaraha jinis jam. Pelanggaran waktos sapertos palanggaran setelan sareng tahan waktos henteu aya gunana tanpa kendala jam.

- Watesan Tunda Input sareng Output - Input jeung Kaluaran reureuh ngajadikeun sangu pikeun jalur reureuh éksternal FPGA. Konstrain ieu bagian tina sarat anggaran reureuh.

- Pangecualian - Nalika desain gagal nyumponan sarat waktos, anjeun panginten peryogi konstrain anu langkung maju pikeun nyangking desain ka panutupan waktos. Lamun dilarapkeun ka jalur husus dina rarancang, éntitas timing ieu override kabiasaan standar Synplify Pro nalika jalur timing ieu dianggap salila optimasi.

Sateuacan ngalebetkeun konstrain, kompilasi heula desain dina Synplify Pro (Run> Compile Only). Ngalaksanakeun kompilasi di jero Synplify Pro tos populates SCOPE sareng nami obyék. Ieu tiasa ngahemat waktos sareng usaha anjeun pikeun ngalebetkeun nami obyék.

- Identifier Awalan Dirojong ku SCOPE sareng FDC

Synplify Pro nganggo identifier obyék anu ditetepkeun dina tabel di handap ieu pikeun konstrain anu ditetepkeun dina SCOPE atanapi FDC files (Tabel 2-2).

Méja 2-2 Identifier Awalan jeung Objék DesainIdentifier Awalan (FDC) SDC Sarua Objék Desain pikeun diterapkeun v: ngaran_design n/a modul c: clock_name get_clocks Jam i: instance_name get_cells instansi p: port_name get_ports Palabuhan t: pin_name get_pins Palabuhan hirarkis atanapi pin sél instantiated b: bus_name get_pins Bit beus n: net_name get_nets Ngaran net - Watesan jam

Aya dua jinis konstrain jam: create_clock sareng create_generated_clock. SCOPE boga dua tab misah pikeun dua konstrain ieu.

Anggo tab Jam pikeun ngaidentipikasi sumber jam (create_clock). Tingal Gambar 2-4.

Paké tab Jam dihasilkeun pikeun ngaidentipikasi jam dihasilkeun (create_generated_clock) dina rarancang. Tingal Gambar 2-5.

Pikeun desain RTG4:- Osilator atanapi palabuhan Input Jam mangrupikeun sumber jam anu khas.

- Kaluaran CCC lawon mangrupikeun jam anu dibangkitkeun khas.

Synplify Pro ngadukung fitur salinan sareng témpél canggih. Kasebut nyaéta dimungkinkeun pikeun nyalin objék tina schematic nu views jeung nempelkeun ngaran maranéhanana kana RUANG.

Pikeun example: Nyorot pin terminal kaluaran osilator (dina RTL view schematic), nyalin (CTRL + C) lajeng nempelkeun (CTRL + V) kana lingkup.

- I / O Watesan reureuh

Konstrain jam teu cukup pikeun konstrain I / O port. Paké input sarta kaluaran reureuh konstrain

(set_input_delay, set_output_delay) konstrain pikeun nangtukeun I / O konstrain. Arahkeun ka tab Inputs/Outputs di RUANGKUNG pikeun ngalakukeunana (Gambar 2-6).

- Pamariksaan Konstrain

Pikeun mariksa konstrain anu diasupkeun sajauh ieu, klik tombol Pariksa Konstrain dina bar ménu. Synplify Pro ngahasilkeun laporan cék konstrain jam (*_cck.rpt). Ringkesan kedah nunjukkeun yén teu aya masalah anu kapendak sareng konstrain waktos.

Pamariksaan Konstrain ogé tiasa diaksés tina ménu Proyék (Proyék> Jalankeun> Pariksa Konstrain). - Pangecualian

Sababaraha desain ngabutuhkeun konstrain waktos tambahan anu katelah pengecualian waktos, sapertos:- set_false_path

- set_max_delay

- set_multicycle_path

Pikeun ngasupkeun pangecualian waktu dina RUANG, arahkeun ka tab Jalur Tunda. Saatos nyimpen éta file, ti File menu milih Tutup pikeun mulang ka Proyék view.

- Ngagunakeun Maju Annotated SDC

Saatos sintésis, Synplify Pro ngahasilkeun SDC file nu bisa Anjeun pake pikeun léngkah sésana dina aliran Libero. Ieu file (kalayan extension *_sdc.sdc) sadia dina Konstrain Timing dina Project Libero view.

Sacara standar, ieu file teu dipaké ku Libero. Aliran anu disarankeun nyaéta nyiptakeun konstrain anu misah pikeun Sintésis sareng léngkah-léngkah Tempat sareng Rute anu Didorong Timing.

Pamaké kudu ulangview éta file eusi Synplify dihasilkeun maju annotated file sateuacan ngaktipkeun file pikeun palaksanaan. Pikeun ngaktipkeun SDC file pikeun Timing-disetir Tempat jeung Rute,-klik katuhu dina file tur pilih Paké pikeun Compile. Libero migunakeun SDC ieu file pikeun léngkah sésana dina aliran desain, mimitian ti Compile. - Watesan

- Maju annotated SDC file ti Synplify Pro henteu kalebet set_clock_latency konstrain anu aya dina SDC pangguna asli file.

- Synplify Pro henteu otomatis ngahasilkeun konstrain jam pikeun osilator atanapi instansi CCC. Anjeun kudu nyadiakeun konstrain jam akurat (create_clock, create_generated_clock) pikeun Synplify Pro. Konstrain ieu lajeng diteruskeun annotated dina *_sdc.sdc file.

Watesan waktos pikeun Tempat sareng Rute anu Didorong Timing

Alat Libero (Timing Driven Place and Route and SmartTime) ngarojong sawaréh tina Synopsys SDC timing konstrain relevan pikeun desain FPGA. Pikeun nyetel watesan waktos, anjeun tiasa nganggo:

- SmartTime Konstrain Wizard

- SmartTime Konstrain Editor

- SDC file(s)

Pikeun ngatur watesan waktos files, nganggo "Atur Konstrain Files" kotak dialog. Nalika ngimpor SDC file pikeun Timing Didorong Tempat jeung Rute, pastikeun pikeun ngawengku eta pikeun pamakéan ku alat Compile. Pikeun ngaktipkeun SDC file geus diimpor di Libero,-klik katuhu dina file tur pilih Paké pikeun Compile (tingali Gambar 2-7).

- Timing-disetir Tempat jeung Konstrain Rute

Analisis Timing SmartTime ngadukung set konstrain waktos SDC ieu:- create_clock

- create_generated_clock

- set_input_delay

- set_output_delay

- set_external_clock

- set_clock_to_output

- set_false_path

- set_multicycle_path

- set_max_delay

- set_min_delay

- set_clock_latency

- set_clock_uncertainty

- set_disable_timing

Pikeun detil ngeunaan pilihan sareng alesan paréntah SDC, tingal pitulung online SmartTime.

- Watesan pikeun Sarat Desain

Microsemi nyarankeun yén anjeun nganggo aliran di handap ieu pikeun ngalebetkeun konstrain waktos:- SmartTime Konstrain Wizard - Identipikasi jam, asupan jeung kaluaran reureuh konstrain

- Editor Atribut I / O - Nyadiakeun inpormasi atribut I / O lengkep pikeun desain

- Ngahasilkeun sareng nganalisis laporan Cakupan Konstrain

- SmartTime Konstrain Wizard

SmartTime kalebet Wizard Konstrain anu ngamungkinkeun éntri gancang sareng gampang pikeun konstrain jam sareng I / O (Gambar 2-8).

Nelepon Wizard Konstrain tina SmartTime (Alat> Wizard Konstrain). The Constraint Wizard ngamungkinkeun anjeun pikeun nambahkeun konstrain dina urutan ieu:- Gemblengna konstrain jam

- Gemblengna I / O konstrain

- Watesan jam spésifik

- Dihasilkeun konstrain jam

- Watesan input spésifik

- Konstrain kaluaran husus

Anggo tab konstrain Gemblengna pikeun nyetél konstrain standar pikeun jam sareng I / OS.

Konstrain standar tiasa ditimpa ku konstrain spésifik pikeun jam sareng I/Os.

- Watesan jam

Anggo jam spésifik sareng tab konstrain jam Dihasilkeun pikeun:- Osilator dipaké salaku sumber jam.

- Output CCC lawon dipaké salaku jam dihasilkeun

- Jam ti sumber séjén

- I/O Watesan

Paké tab Konstrain Gemblengna I / O pikeun set konstrain standar pikeun sakabéh input sarta kaluaran palabuhan dina rarancang. Konstrain I/O standar tiasa ditimpa dina tab Konstrain Input Spésifik sareng Output Spésifik pikeun palabuhan anu dipilih.

Pikeun detil ngeunaan Wizard Konstrain, tingal pitulung online SmartTime. - Atribut I/O jeung Editor Atribut I/O

Kinerja timing jalur I / O sacara signifikan dipangaruhan ku atribut I / O.

Paké fitur I / O Atribut Editor dina MultiView Alat Navigator (MVN) pikeun nyayogikeun inpormasi atribut I / O lengkep pikeun desain.

Pikeun detil ngeunaan Éditor Atribut I/O, tingal MultiView Navigator pitulung online. - Panutup Konstrain

Penting pikeun ngahasilkeun Laporan Cakupan Konstrain (Gambar 2-9), sabab laporan waktos ngan ukur nganalisa kinerja timing pikeun jalur desain sareng konstrain waktos. Jalur waktos tanpa watesan waktos tiasa gaduh palanggaran waktos sareng henteu dilaporkeun. Nyuhunkeun laporan Cakupan Konstrain ti SmartTime Analyzer (Alat > Laporan > Cakupan Konstrain).

Desain jalur atawa objék kalawan kendala leungit dibéréndélkeun di handapeun Saran Enhancement. Review unggal saran jeung suplai konstrain luyu pikeun mastikeun yén sakabéh jalur design gaduh konstrain timing.

Pikeun detil ngeunaan Laporan Cakupan Konstrain, tingal pitulung online SmartTime. - Watesan pikeun Ngaoptimalkeun Desain Anjeun

Konstrain timing desain meureun perlu dioptimalkeun lamun desain gagal minuhan sarat waktu, sanajan sanggeus completing Timing Driven Place and Route (TPDR).

Aliran anu disarankeun pikeun ngaoptimalkeun konstrain desain nyaéta:- Jalankeun Timing Didorong Tempat sareng Rute. Pastikeun yén pilihan Timing-disetir diaktipkeun salila Tempat jeung Rute.

- Ngahasilkeun sareng mariksa laporan Analisis Timing. Nganalisis laporan Analisis Tunda Maksimum sareng Minimum.

- Buka SmartTime Constraints Editor sareng nyayogikeun konstrain tambahan, kalebet pengecualian waktos.

- Pikeun ningkatkeun Performance Placer:

- Debug jalur desain kalayan palanggaran waktos.

- Anggo set_max_delay pikeun ngawatesan jalur domain antar-jam.

- Ngagunakeun Timing Driven Place and Route (TDPR)

Tujuan utama TDPR nyaéta pikeun minuhan konstrain waktos. Upami anjeun henteu milih pilihan anu didorong ku waktos, Tempat sareng Rute moal nganggap watesan waktos.

Pastikeun yén Timing-disetir dipilih sateuacan ngajalankeun Tempat sareng Rute (klik katuhu Tempat sareng Rute sareng pilih Konpigurasikeun Pilihan dina suite alat Libero). Pilihan ieu dipilih sacara standar pikeun RTG4. - Laporan Analisis Timing

SmartTime ngahasilkeun dua jinis laporan waktos sacara standar pikeun analisis Max sareng Min Delay:-

- Laporan waktos - Laporan ieu nunjukkeun inpormasi waktos anu diatur ku domain jam.

- Laporan pelanggaran timing - Laporan slack datar ieu nyayogikeun inpormasi ngeunaan palanggaran konstrain. Pikeun ngahasilkeun laporan analisis waktos di Libero, klik katuhu Verify Timing tur pilih Run.

- Eusi Laporan Timing

Laporan waktos ngandung bagian-bagian ieu:- Header - daptar jinis laporan, versi, tanggal sareng waktos laporan sareng inpormasi desain umum

- Ringkesan - ngalaporkeun inpormasi waktos pikeun tiap domain jam

- Pamilihan Jalur - daptar inpormasi waktos pikeun sababaraha jinis jalur dina desain. Pikeun detil, tingal pitulung online SmartTime.

- Eusi Laporan Pelanggaran Timing

Laporan palanggaran waktos ngandung bagian-bagian ieu: - lulugu

Daptar lulugu:- Jenis laporan

- Vérsi SmartTime dipaké pikeun ngahasilkeun laporan

- Tanggal sareng waktos laporan didamel

- Inpormasi desain umum (ngaran, kulawarga, jsb.)

- jalur

Bagian jalur daptar inpormasi waktos pikeun jalur anu dilanggar dina desain.

Sacara standar, bangbarung slack nyaéta 0 sareng jumlah jalur diwatesan. Jumlah maksimum standar anu dilaporkeun nyaéta 100.

Sadaya domain jam dicampurkeun dina laporan ieu. Jalur didaptarkeun ku ngirangan slack.

-

- SmartTime Konstrain Editor

SmartTime Constraints Editor mangrupikeun alat anu ngamungkinkeun anjeun nyiptakeun, view sareng édit sadaya watesan waktos desain. Konstrain disayogikeun ngaliwatan wizard konstrain atanapi SDC files sadia pikeun ngédit dina SmartTime Konstrain Editor.

Anggo Wizard Konstrain pikeun nyayogikeun konstrain waktos dasar pikeun jam sareng port I/O. Pikeun watesan waktos maju sapertos pengecualian waktos nganggo Editor Konstrain.- Pangecualian Timing

Dumasar pajeulitna desain, pangecualian waktos tiasa diperyogikeun. Pangecualian waktos mangrupikeun konstrain waktos anu disetél dina jalur khusus dina desain. Pikeun example:- set_false_path

- set_max_delay

- set_multicycle_path

Nyadiakeun konstrain ieu merlukeun pangaweruh ngeunaan jalur data dina rarancang jeung sarat timing maranéhanana. Sacara standar, SmartTime nganggo siklus jam tunggal pikeun nganalisa jalur waktos anu ngagaduhan konstrain jam. Iwal timing dipaké pikeun override konstrain jam standar pikeun jalur desain.

Pikeun detil ngeunaan Pangecualian Timing, tingal pitulung online SmartTime.

Catetan: Dumasar severity pelanggaran timing, éta ogé bisa jadi perlu nyadiakeun konstrain pangecualian timing kana software sintésis. Pikeun nyadiakeun konstrain iwal timing kana software sintésis, kaasup konstrain ieu dina FDC file disayogikeun ka Synplify Pro.

- Pangecualian Timing

Ningkatkeun Performance Placer

Nalika desain gagal nyumponan tujuan waktos, jalur desain anu gagal kedah dianalisis sacara saksama. Dua masalah kedah dianalisis:

- Tiasa kinerja timing jalur gagal (s) ningkat lamun panempatan conto ieu dirobah?

Telat rute panjang pikeun jalur desain sareng palanggaran setelan tiasa nunjukkeun yén panempatan instansi henteu optimal. panempatan jalur design bisa nalungtik ngagunakeun alat "Chip Nu Ngarencana", anu mangrupa bagian ti MultiView Navigator. - Dupi konstrain timing cukup pikeun placer pikeun ngaidentipikasi sarta dianggo dina jalur kritis leres dina rarancang?

Pastikeun yén set lengkep konstrain timing dijieun tur dibikeun ka alat placer. Anggo set_max_delay konstrain pikeun leres ngawatesan jalur desain domain antar-jam. Bagian di handap ieu gaduh detil langkung seueur ngeunaan ngalangkungan konstrain sareng nganggo set_max_delay konstrain.

- Performance Placer - Konstrain dirojong

Anjeun tiasa ngalangkungan konstrain waktos ka Placer ku:- Ngatur wates waktu files ngagunakeun Konstrain Atur Files kotak dialog. Nalika ngimpor SDC file pikeun placer nu, pastikeun kaasup eta pikeun pamakéan ku alat Compile. Pikeun ngaktipkeun SDC file geus diimpor kana Libero, klik katuhu dina file tur pilih Paké pikeun Compile.

- Lebetkeun konstrain dina SmartTime GUI - Upami nganggo skenario, pastikeun yén skenario diaktipkeun pikeun TDPR.

- Watesan

- Placer ayeuna ngadukung konstrain ieu:

- create_clock

- create_generated_clock

- set_clock_latency

- set_input_delay

- set_output_delay

- set_max_delay

- set_false_path

- Watesan di handap ieu henteu dirojong ku anu nempatkeun:

- set_clock_uncertainty

- set_multicycle_path

- set_min_delay

- Placer henteu ngadukung waktos domain antar-jam. Placer ngaoptimalkeun jam dina domain maranéhanana, tapi teu antara domain. Pikeun ngaktipkeun optimasi placer pikeun jalur domain antar-jam, make set_max_delay konstrain. Ieu dijelaskeun dina bagian salajengna.

- placer nu teu kaasup jalur generasi jam dina datangna / merlukeun itungan waktu nalika set_max_delay Konstrain dipaké.

- Placer ayeuna ngadukung konstrain ieu:

- Ngagunakeun set_max_delay pikeun Ngaronjatkeun Hasil Placer

Ieu mungkin pikeun ngaronjatkeun hasil placer ku ngagunakeun set_max_delay timing konstrain on jalur desain jeung palanggaran timing. Mertimbangkeun ngagunakeun pendekatan ieu lamun jalur violating:-

- Nyaéta jalur domain antar-jam.

- Ngandung telat generasi jam anu béda sacara signifikan antara titik awal sareng tungtung.

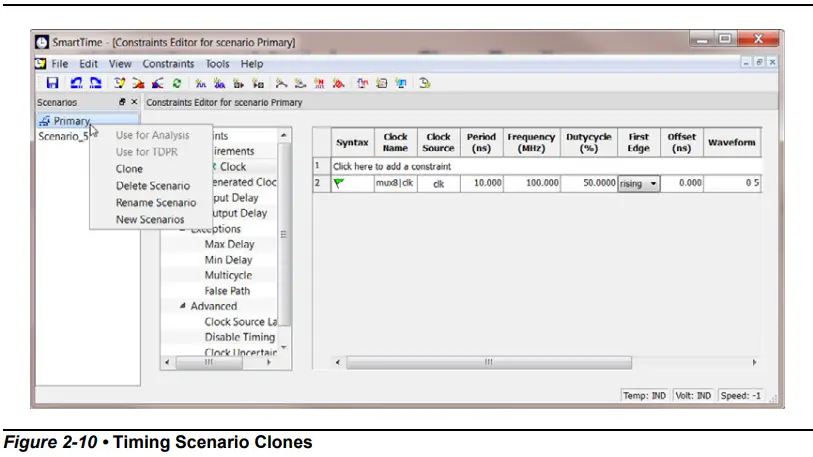

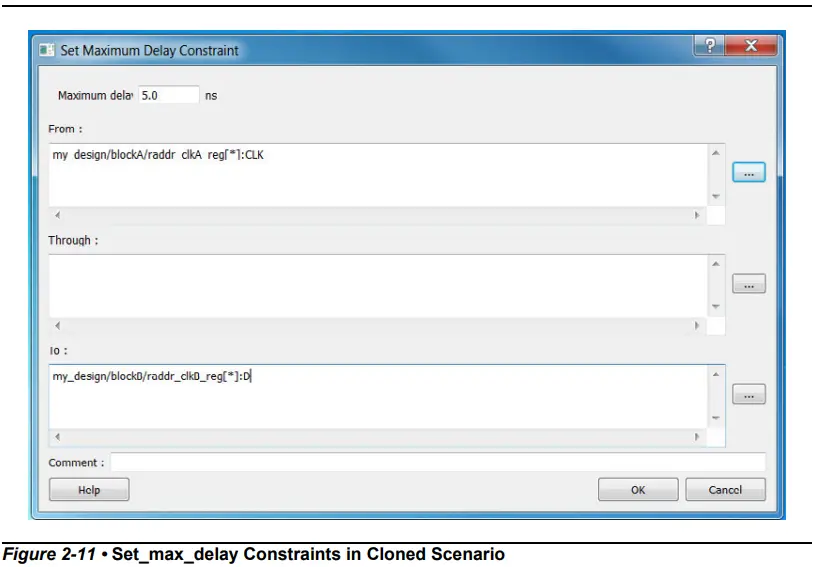

- Pikeun nyertakeun watesan waktos tambahan pikeun placer:

- Kloning skenario konstrain waktos anu aya di SmartTime. Tina Constraint Editor, klik-katuhu Skenario primér sareng pilih Klon (Gambar 2-10).

- Pertahankeun set konstrain aslina (Primer) pikeun analisa waktos

- Lebetkeun set_max_delay konstrain pikeun jalur desain anu meuntas domain jam (gambar 2-11).

- Paké set kadua konstrain (skenario kloning) éksklusif pikeun TDPR. Klik-katuhu skenario Kloning tur pilih Paké pikeun TDPR (Gambar 2-12).

- Kloning skenario konstrain waktos anu aya di SmartTime. Tina Constraint Editor, klik-katuhu Skenario primér sareng pilih Klon (Gambar 2-10).

-

Pikeun detil ngeunaan set_max_delay konstrain, tingal pitulung online SmartTime.

Konstrain pikeun RTG4 IP Blok

Bab ieu ngajelaskeun sarat watesan pikeun blok di handap ieu:

- Osilator

- Sirkuit Pengkondisian Jam Fabric (CCC)

- Antarmuka Serial Laju Luhur (SERDES)

Osilator

Osilator ngan boga hiji kaluaran CLKOUT 50 MHz. Kaluaran ngan ukur tiasa disambungkeun ka CCC configurator.

- Watesan Sintésis osilator

Anjeun kudu nangtukeun konstrain jam pikeun osilator dipaké ku desain.

angka 3-2 nembongkeun blok sakumaha katingal ku sintésis.

Konstrain di handap ieu bakal dianggo pikeun osilator sareng RCOSC_50MHZ_0 salaku nami conto. The osilator RC geus ngonpigurasi pikeun 50 MHz.

create_clock -ngaran osc_50MHz -period 20 \

[get_pins { RCOSC_50MHZ_0.CLKOUT}] - Osilator Tempat jeung Konstrain Rute

Pikeun SmartTime, watesan pikeun konfigurator osilator disambungkeun kana conto CCC RTG4FCCC_0 nyaéta:

create_clock -name osc_50MHz -period 20 [get_pins {RCOSC_50MHZ_0:CLKOUT}]

Sirkuit Pengkondisian Jam Kain RTG4 (CCC)

CCCs dipaké pikeun ngalikeun, ngabagi atawa reureuh jam. Pangaruh maranéhanana dijelaskeun pangalusna ngagunakeun jam dihasilkeun.

- RTG4 lawon CCC Sintésis Konstrain

Pikeun nyieun konstrain RTG4FCCC pikeun sintésis via jam dihasilkeun, anjeun kudu make RTG4FCCC sababaraha sarta ngabagi faktor. Inpo ieu sadia dina tab Advanced dina CCC Configurator diaksés ngaliwatan software Libero (gambar 3-3).

Konfigurasi CCC ditémbongkeun dina Gambar 3-3 ngahasilkeun opat jam:- Dina GL0, jam 150 MHz dihasilkeun tina jam input 50 MHz ngagunakeun PLL.

- Dina GL1, a 200 MHz dihasilkeun tina PLL sarua

- Dina GL2, jam 25 MHz dihasilkeun tina osilator 50 MHz.

- Dina GL3, jam 100MHz dihasilkeun tina CLK3_PAD sareng CLK_PAD2.

Faktor division jeung multiplication pasti bisa diitung dumasar kana konfigurasi divider ditémbongkeun dina configurator nu. Faktor anu digunakeun pikeun GL0 dikurilingan. Nalika CCC dipaké, faktor multiplication dirumuskeun ku divider eupan balik (dikurilingan ku biru); faktor division dirumuskeun ku cara ngalikeun divider rujukan (circled beureum) jeung kaluaran (GPD) divider (circled di héjo).

Jam dihasilkeun pakait nyaéta:

create_clock -name CLK0_PAD -period 20 [get_pins {RTG4FCCC_0.CLK0_PAD}] create_clock -name CLK2_PADP -periode 10 [get_pins {RTG4FCCC_0.CLK2_PADP}] create_clock -name CLK3_PADP -period 10 {RTG4FCCC_0.CLK3_PADP}] create_generated_clock -ngaran clk_150mhz -divide_by 16 -multiply_by 24 \

-sumber [get_pins {RTG4FCCC_0.CLK0_PAD}] \

[get_pins {RTG4FCCC_0.GL0}] create_generated_clock -ngaran clk_200mhz -divide_by 12 -multiply_by 24 \

-sumber [get_pins {RTG4FCCC_0.CLK0_PAD}]\

[get_pins {RTG4FCCC_0.GL1}] create_generated_clock -ngaran clk_25mhz -divide_by 2 \

-sumber [get_pins { RTG4FCCC_0.RCOSC_50MHZ}] \

[get_pins {RTG4FCCC_0.GL2}] create_generated_clock -ngaran clk_100mhz -divide_by 1 -multiply_by 1 \

-sumber [get_pins {RTG4FCCC_0.CLK2_PADP}] \

[get_pins {RTG4FCCC_0.GL3}]

- RTG4 lawon CCC Tempat jeung Konstrain Rute

Pikeun SmartTime, konstrain pikeun CCC configurator nyaéta:

create_clock -ngaran CLK0_PAD -period 20 [get_ports {CLK0_PAD}] create_clock -name CLK2_PADP -period 10 [get_ports {CLK2_PADP}] create_clock -name CLK3_PADP -period 10 [get_ports {CLK3_PAlk_DP_}c create_generate

-bagi_ku 16 \

-kalikeun_ku 24 \

-sumber {RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK0_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL0}

create_generated_clock -ngaran clk_200mhz \

-bagi_ku 12 \

-kalikeun_ku 24 \

-sumber {RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK0_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL1}

create_generated_clock -ngaran clk_25mhz \

-bagi_ku 2 \

-sumber {RTG4FCCC_0/CCC_INST/INST_CCC_IP:RCOSC_50MHZ} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL2}

create_generated_clock -ngaran clk_100mhz \

-bagi_ku 1 \

-kalikeun_ku 1 \

-sumber {RTG4FCCC_0/CCC_INST/INST_CCC_IP:CLK2_PAD} \

{RTG4FCCC_0/CCC_INST/INST_CCC_IP:GL3}

High Speed Serial Interface (SERDES) Blok

Blok panganteur serial speed tinggi atawa panganteur serializer / deserializer (SERDESIF) integrates sababaraha blok fungsi pikeun ngarojong sababaraha speed tinggi protokol serial dina FPGA. Blok SERDESIF gaduh fitur ieu:

- Periferal Component Interconnect express (PCIe-PCI Express®) rojongan protokol

- 10 Gigabit Attachment Unit Interface (XAUI) rojongan protokol

- Antarbeungeut Sub-lapisan Coding Fisik éksternal (EPCS) ngadukung protokol séri kacepetan luhur anu didefinisikeun ku pangguna, sapertos dukungan protokol antarmuka bebas média Gigabit séri (SGMII).

Modeu protokol serial tunggal atawa Dual operasi. Dina modeu protokol serial Dual, dua protokol bisa dilaksanakeun dina opat jalur fisik komunikasi blok SERDESIF blok SERDESIF ka lawon FPGA ngaliwatan panganteur AXI/AHBL atawa panganteur EPCS.

- Modeu Protokol PCI Express

Dina modeu ieu, blok SERDESIF komunikasi sareng FPGA nganggo antarmuka AXI / AHBL sareng Antarmuka APB3 pikeun konfigurasi; euweuh konstrain husus pikeun blok ieu diperlukeun. - Modeu Protokol EPCS

Dina modeu EPCS, SERDESIF tiasa ngadukung dugi ka opat jalur. Dina modeu EPCS, blok SERDESIF ngagunakeun tilu jam:- APB_S_PCLK pikeun beus konfigurasi APB3

- EPCS_0_RXFWF_RCLK pikeun nampa data laleur kabayang panganteur lawon fifo

- EPCS_0_TXFWF_WCLK pikeun ngirimkeun data ngapung kabayang panganteur lawon fifo

Jam APB_S_PCLK, EPCS_0_RXFWF_RCLK sareng EPCS_0_TXFWF_WCLK kedah ditetepkeun dina sumberna. Taya konstrain husus pikeun blok ieu diperlukeun.

- Modeu Protokol XAUI

Dina modeu XAUI, blok SERDESIF ngagunakeun lima jam:- REFCLK_P - Input pikeun TxPLL

- APB_S_CLK pikeun beus konfigurasi APB3

- XAUI_MMD_MDC salaku jam panganteur MDIO

- XAUI_RX_CLK_IN - Data anu ditampi disingkronkeun dina flywheel FIFO kana jam ieu

- XAUI_TX_CLK_OUT - Data dikirimkeun nyaéta sampdipingpin ku jam singkronisasi lamun santunan jam diaktipkeun. XAUI_TX_CLK_OUT kudu disambungkeun ka XAUI_FB_CLK pikeun ngaktipkeun santunan jam.

Jam REFCLK_P, APB_S_PCLK, XAUI_MMD_MDC sareng XAUI_RX_CLK_IN kedah ditetepkeun dina sumberna.

Jam XAUI_TX_CLK_OUT tiasa didefinisikeun dina palabuhan kaluaran GL0/GL1 tina blok SERDESIF. Mantanample handap nyiptakeun jam ieu duanana NPSS na PCIE SERDES blok.

- Watesan Sintésis XAUI

- NPSS SERDES

create_clock -name {gl_clocks1} \

- période 6.400 \

[meunang_pin {NPSS_SERDES_IF_0.SERDESIF_INST.GL*}] - PCIE SERDES

create_clock -name {gl_clocks2} \

- période 6.400 \

[meunang_pin {PCIE_SERDES_IF_0.SERDESIF_INST.GL*}]

- NPSS SERDES

- XAUI Tempat jeung Konstrain Rute

- NPSS SERDES

create_clock -name {gl_clocks1} \

- période 6.400 \

[meunang_pin {NPSS_SERDES_IF_0/SERDESIF_INST/INST_NPSS_IP:GL*}] - PCIE SERDES

create_clock -name {gl_clocks2} \

- période 6.400 \

[meunang_pin {PCIE_SERDES_IF_0/SERDESIF_INST/INST_PCIE_IP:GL*}

- NPSS SERDES

Rojongan produk

Microsemi SoC Products Group nyokong produkna sareng sababaraha jasa dukungan, kalebet Layanan Pelanggan, Pusat Dukungan Téknis Pelanggan, a websitus, surat éléktronik, sareng kantor penjualan sadunya. Lampiran ieu ngandung inpormasi ngeunaan ngahubungan Microsemi SoC Products Group sareng nganggo jasa dukungan ieu.

Palayanan palanggan

Kontak Service Palanggan pikeun rojongan produk non-teknis, kayaning harga produk, upgrades produk, update informasi, status pesenan, jeung otorisasina.

- Ti Amérika Kalér, nelepon 800.262.1060

- Ti sakuliah dunya, nelepon 650.318.4460

- Fax, ti mana waé di dunya, 408.643.6913

Customer Téknis Rojongan Center

Microsemi SoC Products Group staffs Pusat Dukungan Téknis Pelanggan sareng insinyur anu terampil anu tiasa ngabantosan ngajawab patarosan hardware, software, sareng desain anjeun ngeunaan Produk Microsemi SoC. Pusat Pangrojong Téknis Pelanggan nyéépkeun waktos anu ageung pikeun nyiptakeun catetan aplikasi, jawaban kana patarosan siklus desain umum, dokuméntasi masalah anu dipikanyaho, sareng sagala rupa FAQ. Janten, sateuacan ngahubungi kami, mangga buka sumber online kami. Sigana pisan kami parantos ngajawab patarosan anjeun.

Bantosan Téknis

Nganjang ka Rojongan Palanggan websitus (www.microsemi.com/soc/support/search/default.aspx) kanggo inpormasi sareng dukungan langkung seueur. Loba jawaban sadia dina searchable web sumberdaya ngawengku diagram, ilustrasi, sarta tumbu ka sumber sejenna dina websitus.

Websitus

Anjeun tiasa ngotéktak rupa-rupa informasi teknis jeung non-teknis dina kaca imah SoC, di www.microsemi.com/soc.

Ngahubungan Pusat Rojongan Téknis Pelanggan

Insinyur anu terampil pisan staf Pusat Rojongan Téknis. Pusat Dukungan Téknis tiasa dikontak ku email atanapi ngalangkungan Microsemi SoC Products Group websitus.

Surélék

Anjeun tiasa ngahubungkeun patarosan téknis anjeun ka alamat email kami sareng nampi jawaban deui ku email, fax, atanapi telepon. Ogé, upami anjeun gaduh masalah desain, anjeun tiasa email desain anjeun files pikeun nampa bantuan. Urang terus ngawas akun surelek sapopoe. Nalika ngirim pamundut anjeun ka kami, punten pastikeun kalebet nami lengkep anjeun, nami perusahaan, sareng inpormasi kontak anjeun pikeun ngolah pamundut anjeun sacara efisien.

Alamat email dukungan téknis nyaéta soc_tech@microsemi.com.

Kasus abdi

Palanggan Microsemi SoC Products Group tiasa ngalebetkeun sareng ngalacak kasus téknis sacara online ku jalan ka My Cases.

Luar AS

Konsumén anu peryogi bantosan di luar zona waktos AS tiasa ngahubungi dukungan téknis via email (soc_tech@microsemi.com) atanapi ngahubungan kantor penjualan lokal. listings kantor jualan bisa kapanggih dina www.microsemi.com/soc/company/contact/default.aspx.

Rojongan Téknis ITAR

Pikeun rojongan teknis ngeunaan RH jeung RT FPGAs nu diatur ku International Traffic in Arms Regulations (ITAR), ngahubungan kami via soc_tech_itar@microsemi.com. Alternatipna, dina Kasus Kuring, pilih Sumuhun dina daptar turun-handap ITAR. Pikeun daptar lengkep ngeunaan Microsemi FPGAs ITAR-diatur, buka ITAR web kaca.

Microsemi Corporation (Nasdaq: MSCC) nawiskeun portopolio komprehensif semikonduktor sareng solusi sistem pikeun komunikasi, pertahanan sareng kaamanan, aerospace, sareng pasar industri. Produk kaasup-kinerja tinggi jeung radiasi-hardened analog dicampur-sinyal terpadu sirkuit, FPGAs, SoCs, sarta ASICs; produk manajemén kakuatan; waktos sareng alat singkronisasi sareng solusi waktos anu tepat, netepkeun standar dunya pikeun waktos; alat ngolah sora; solusi RF; komponén diskrit; téhnologi kaamanan sarta scalable anti-tamper produk; Power-over-Ethernet ICs sareng midspans; kitu ogé kamampuhan design custom sarta jasa. Microsemi kantor pusatna di Aliso Viejo, California sareng gaduh sakitar 3,400 karyawan sacara global. Diajar langkung seueur di www.microsemi.com.

Markas Perusahaan Microsemi

Hiji perusahaan, Aliso Viejo CA 92656 AS

Di jero AS: +1 800-713-4113

Luar AS: +1 949-380-6100

Penjualan: +1 949-380-6136

Fax: +1 949-215-4996

Surélék: sales.support@microsemi.com

©2015 Microsemi Corporation. Sadaya hak disimpen. Microsemi jeung logo Microsemi mangrupakeun mérek dagang ti

Microsemi Corporation. Sadaya merek dagang sareng merek jasa sanés mangrupikeun hak milik nu gaduhna.

Dokumén / Sumberdaya

|

Microsemi RTG4 FPGA Watesan Timing [pdf] Pituduh pamaké RTG4 FPGA Watesan waktos, RTG4 FPGA, Watesan waktos, Watesan |